NOTICE: This document contains references to Agilent Technologies. Agilent's former Test and Measurement business has become Keysight Technologies. For more information, go to **www.keysight.com.**

IC-CAP 2012.01 January 2012 Simulation

# © Agilent Technologies, Inc. 2000-2011

3501 Stevens Creek Blvd., Santa Clara, CA 95052 USA

No part of this documentation may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

# **Acknowledgments**

**UNIX** ® is a registered trademark of the Open Group.

**MS-DOS** @, Windows @, and MS Windows @ are U.S. registered trademarks of Microsoft Corporation.

**Pentium** ® is a U.S. registered trademark of Intel Corporation.

**PostScript**® is a trademark of Adobe Systems Incorporated.

**Java**<sup>™</sup> is a U.S. trademark of Sun Microsystems, Inc.

**Mentor Graphics** is a trademark of Mentor Graphics Corporation in the U.S. and other countries.

Qt Version 4.6

**Ot Notice**

The Qt code was modified. Used by permission.

# **Qt Copyright**

Qt Version 4.6, Copyright (c) 2009 by Nokia Corporation. All Rights Reserved.

**Qt License** Your use or distribution of Qt or any modified version of Qt implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included.

**Qt Availability** <a href="http://www.qtsoftware.com/downloads">http://www.qtsoftware.com/downloads</a>

Patches Applied to Qt can be found in the installation at: \$HPEESOF DIR/prod/licenses/thirdparty/qt/patches.

You may also contact Brian Buchanan at Agilent Inc. at brian\_buchanan@agilent.com for more information. For details see:

http://bmaster.soco.agilent.com/mw/Qt License Information

**Errata** The IC-CAP product may contain references to "HP" or "HPEESOF" such as in file names and directory names. The business entity formerly known as "HP EEsof" is now part of Agilent Technologies and is known as "Agilent EEsof." To avoid broken functionality and to maintain backward compatibility for our customers, we did not change all the names and labels that contain "HP" or "HPEESOF" references.

#### Simulation

**Warranty** The material contained in this documentation is provided "as is", and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

**Technology Licenses** The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

**Restricted Rights Legend** U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

# Simulation

| IC-CAP Simulation Overview               |     |

|------------------------------------------|-----|

| Simulation Types                         | 7   |

| Simulation Input and Output Requirements | 8   |

| Performing a Simulation                  | 21  |

| Using Simulation Debugger                | 30  |

| Linking a Simulator to IC-CAP            | 33  |

| Adding a Simulator                       | 34  |

| Remote Simulation                        | 42  |

| Simulators in IC-CAP                     |     |

| ADS Simulator                            |     |

| SPECTRE Simulator                        | 106 |

| HSPICE Simulator                         |     |

| SPICE Simulators                         | 119 |

| Eldo Simulator                           | 137 |

| Saber Simulator                          | 140 |

# **IC-CAP Simulation Overview**

Simulation in IC-CAP is the process of generating device and circuit output characteristics based on an available model. The accuracy of a model determines how simulated characteristics agree with the real physical behavior of devices and circuits.

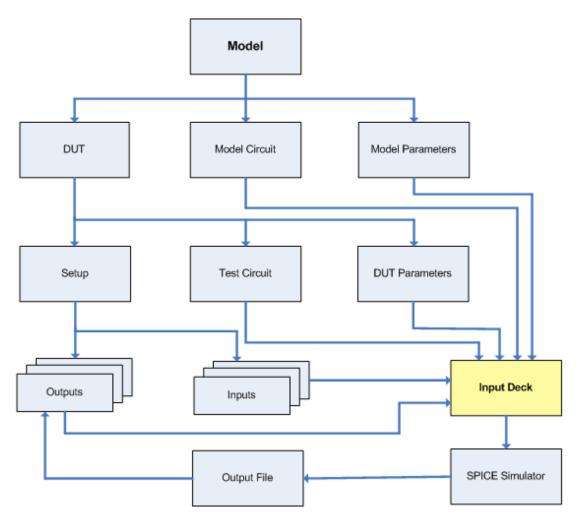

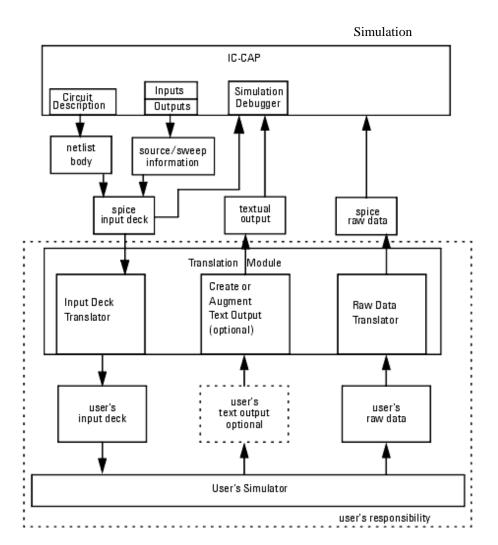

The following figure illustrates the IC-CAP simulation process.

**Figure: Simulation Flow Diagram**

You can use five types of simulators in IC-CAP:

- · Advanced Design System (ADS) simulator

- SPICE simulators

- HSPICE simulator

- Saber simulator

For details on types of simulators you can use with IC-CAP, refer to *Simulators in IC-CAP* (simulation).

# **1** Notes

- 1. The PC version of IC-CAP supports ADS version 2002 or newer. Older versions of ADS cannot be used with the PC version of IC-CAP.

- 2. Simulators are provided with IC-CAP as a courtesy and are not supported by Agilent Technologies except the ADS simulator.

#### **Simulation Interfaces**

Simulation Interfaces, also known as *templates*, are provided with the simulators. The IC-CAP simulator interface is an open system. It allows you to add any simulator which is similar to one of the provided templates. For details on adding a simulator, refer to *Adding a Simulator* (simulation) section.

The following table lists the IC-CAP Supported Simulators and Corresponding Template Names.

| Simulator                    | Template Name                                                     |

|------------------------------|-------------------------------------------------------------------|

| UCB SPICE2G.6                | spice2                                                            |

| UCB SPICE3E2                 | spice3                                                            |

| HPSPICE                      | hpspice                                                           |

| HSPICE                       | hspice                                                            |

| ELDO                         | eldo                                                              |

| Saber                        | saber                                                             |

| SPECTRE                      | spectre (native circuit syntax) spectre443 (spice circuit syntax) |

| Advanced Design System (ADS) | hpeesofsim (native circuit syntax)                                |

# **Simulation Types**

IC-CAP supports eight basic types of simulation which can be categorized as:

- Standard Simulation

- Special Simulation

### **Standard Simulation**

Standard simulation types are available in the SPICE simulators and include the following:

- DC simulation

- AC simulation

- Transient simulation

- Noise simulation

# **Special Simulation**

The special simulation types include:

- Capacitance Voltage (CV) simulation

- 2-Port (S,H,Y,Z,K,A parameter) simulation

- Multiport (S parameter) simulation

- Time-Domain Reflectometry (TDR) simulation

- Harmonic Balance simulation

# **1** Note

Special simulations are not directly available in the SPICE simulators. IC-CAP builds an additional circuitry required in the simulator input files to perform the simulation.

Running a simulation with input and output specifications that do not match with the simulation types could result in the following error:

```

ERROR: Unable to simulate.

Check the Input and Output specifications.

```

The simulators interfaced with IC-CAP may only support a subset of these simulation types and not all of the analysis types available in a particular simulator. For example, non-electrical analysis for Saber is not supported, and Harmonic Balance is supported only with the ADS simulators.

For detailed information on the types of simulation that each simulator supports, refer to the following topics:

- SPICE Simulators (simulation)

- SPECTRE Simulator (simulation)

- Saber Simulator (simulation)

- ADS Simulator (simulation)

#### See Also

# Simulation

Simulation Input and Output Requirements (simulation)

# **Simulation Input and Output Requirements**

This section describes the input and output specifications required for a valid setup for each simulation type and the corresponding measurement types.

- DC Simulation

- AC Simulation

- Transient Simulation

- Noise Simulation

- CV Simulation

- 2-Port Simulation

- Multiport Simulation

- TDR Simulation

- Harmonic Balance Simulation

# **DC Simulation**

The following table describes the input and output specifications required for a valid setup for DC simulation.

| INPUT MODE | VALID SWEEPS              | VALID OUTPUTS |

|------------|---------------------------|---------------|

| V          | LIN, LOG, LIST, SYNC, CON | V, I          |

| I          | LIN, LOG, LIST, SYNC, CON | V, I          |

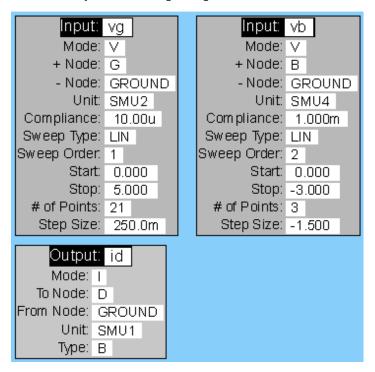

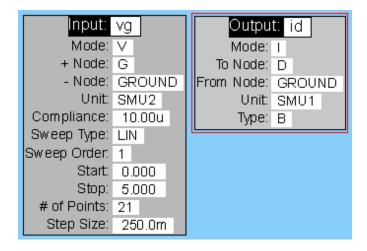

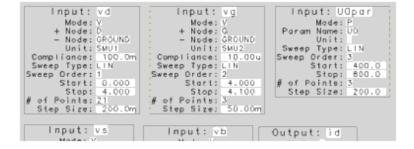

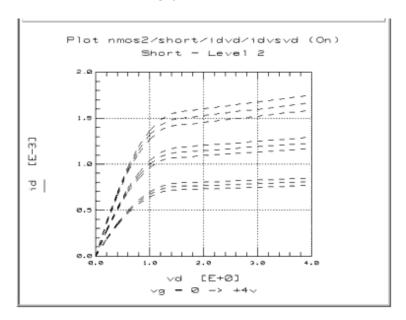

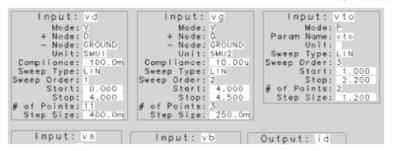

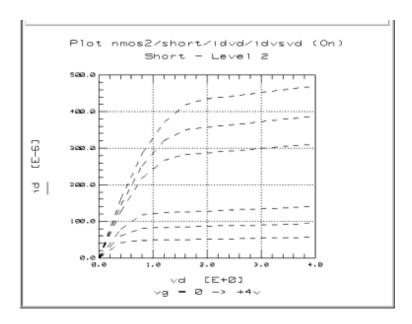

The following figure shows an example of input and output specifications for a MOSFET *id versus vg* setup.

Figure: Example Input and Output, DC Simulation

#### Active Setup: /nmos2/large/idvg

#### **AC Simulation**

The following table describes the input and output specifications required for a valid setup for AC simulation.

| INPUT MODE | VALID SWEEPS                     | VALID OUTPUTS | <b>FOOTNOTES</b> |

|------------|----------------------------------|---------------|------------------|

| V          | LIN, LOG, LIST, SYNC, CON,<br>AC | V, I          | 1, 2, 3          |

| I          | LIN, LOG, LIST, SYNC, CON,<br>AC | V, I          | 1, 2, 3          |

| F          | LIN, LOG, LIST, CON              | V, I          |                  |

- 1. Exactly one frequency sweep required.

- 2. At least one AC source required.

- 3. SYNC is not a valid sweep type when using ADS simulators.

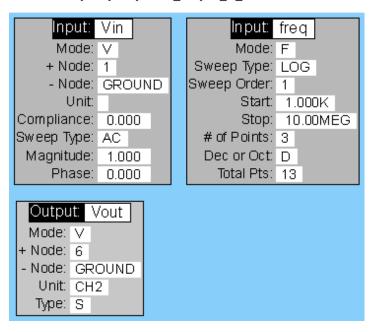

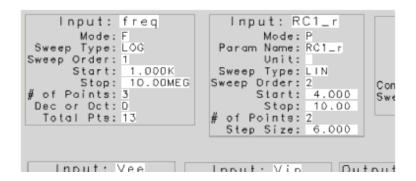

The following figure shows an example of input and output specifications for simulating the output voltage versus frequency of an inverting operational amplifier.

Figure: Example Input and Output, AC Simulation

#### Active Setup: /opamp1/inv\_amp/B\_P\_macro

### **Transient Simulation**

The following table describes the input and output specifications required for a valid setup for Transient simulation.

| INPUT MODE | VALID SWEEPS                                          | VALID OUTPUTS | FOOTNOTES |

|------------|-------------------------------------------------------|---------------|-----------|

| Т          | LIN, LIST, CON                                        | V, I          | 1, 2      |

| V          | LIN, LOG, LIST, SYNC, CON, EXP, PULSE, PWL, SFFM, SIN | V, I          | 1, 2      |

| I          | LIN, LOG, LIST, SYNC, CON, EXP, PULSE, PWL, SFFM, SIN | V, I          |           |

- 1. Exactly one time sweep required.

- 2. LIST sweep not supported with Saber.

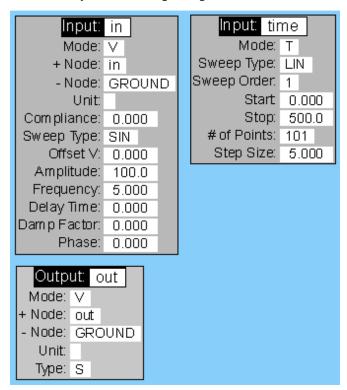

The following figure shows an example of input and output specifications for voltage versus time characteristics of a differential pair.

Figure: Example Input and Output, Transient Simulation

#### Active Setup: /nmos2/large/idvg

### **Noise Simulation**

The following tables describe the input and output specifications required for a valid setup for Noise simulation depending on the simulator being used.

Table: Input and Output Requirements for a Noise Simulation using SPICE Simulators

| INPUT MODE | VALID SWEEPS                     | VALID OUTPUTS | <b>FOOTNOTES</b> |

|------------|----------------------------------|---------------|------------------|

| V          | LIN, LOG, LIST, SYNC, CON,<br>AC | N             | 1, 2, 3          |

| I          | LIN, LOG, LIST, SYNC, CON,<br>AC | N             | 1, 2, 3          |

| F          | LIN, LOG, CON                    | N             | 1, 2, 3          |

- 1. Exactly one noise output required.

- 2. Exactly one frequency sweep required.

- 3. At least one AC source required.

Table: Input and Output Requirements for a Noise Simulation using ADS Simulators

| INPUT MODE | VALID SWEEPS                     | VALID OUTPUTS | FOOTNOTES |

|------------|----------------------------------|---------------|-----------|

| V          | LIN, LOG, LIST, SYNC, CON,<br>AC | N, V, I       | 1, 2, 3   |

| I          | LIN, LOG, LIST, SYNC, CON,<br>AC | N, V, I       | 1, 2, 3   |

| F          | LIN, LOG, SEG, CON               | N, V, I       | 1, 2, 3   |

- 1. There can be multiple outputs.

- 2. Exactly one frequency sweep required.

3. Both V and I Outputs are DC outputs.

#### **CV Simulation**

The following table describes the input and output specifications required for a valid setup for CV simulation.

# 1 Note

The frequency at which the CV simulation is performed can be specified using the System Variable CV\_FREQ in Hz. If this variable is not specified, the simulation is performed at 1-MG (Hz).

| INPUT<br>MODE | VALID SWEEPS                 | VALID OUTPUTS                                                | FOOTNOTES |

|---------------|------------------------------|--------------------------------------------------------------|-----------|

| V             | LIN, LOG, LIST, SYNC,<br>CON | a single C, a single G, a single R, a single X, C + G, C + R | 1, 2      |

| I             | LIN, LOG, LIST, SYNC,<br>CON | a single C, a single G, a single R, a single X, C + G, C + R | 1, 2      |

- 1. Any single output type of C, G, R, or X; or exactly one C and one G; or exactly one C and one R.

- 2. A single C or a C + G is the capacitance using Cp-Gp mode, while a C + R simulates Cs-Rs data

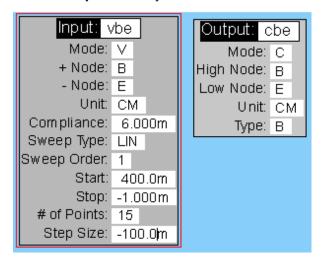

The following figure shows an example of input and output specifications for a BJT baseemitter pn-junction capacitance *versus* voltage setup.

Figure: Example Input and Output, CV Simulation

#### ACtive Setup: /cv/cbe/cje

#### 2-Port Simulation

The following tables describe the input and output specifications required for a valid setup for 2-port simulation.

**Table: Input and Output Requirements for a 2-Port Simulation**

#### Simulation

| INPUT MODE | VALID SWEEPS              | VALID OUTPUTS       | FOOTNOTES     |

|------------|---------------------------|---------------------|---------------|

| F          | LIN, LOG, LIST, CON       | S, H, Y, Z, K, A, F | 1, 2, 3, 4, 5 |

| V          | LIN, LOG, LIST, SYNC, CON | S, H, Y, Z, K, A, F | 1, 2, 3, 4, 5 |

| I          | LIN, LOG, LIST, SYNC, CON | S, H, Y, Z, K, A, F | 1, 2, 3, 4, 5 |

- 1. Exactly one frequency sweep required.

- 2. Exactly one 2-port output (S,H,Y,Z,K, or A) required.

- 3. Only ADS supports F output. (2-Port noise simulation supports ADS only. If the SIMULATOR is not equal to hpeesofsim, the following error message appears. *Error: in "Output xxxx" High frequency noise output is not supported with current simulator.*)

- 4. Exactly one 2-port output required for F output.

- 5. F output can be multiple outputs.

**Table: High Frequency Noise Output and Its Data Type Description**

| F<br>Output  | Name (Output<br>Editor)         | Symbol shown on<br>Setup Page | Description                            | Port Input<br>Requirement |

|--------------|---------------------------------|-------------------------------|----------------------------------------|---------------------------|

| Mode         | High Frequency Noise            | F                             | High frequency noise mode type         |                           |

| Data<br>Type | Noise Figure                    | NF                            | Noise figure data                      | Yes, <sup>1, 2</sup>      |

|              | Gamma Opt                       | GAMMAOPT                      | Optimum source reflection coefficients | No                        |

|              | Equivalent R Noise              | RN                            | Equivalent noise resistance data       | No                        |

|              | Min Noise Figure                | NFMIN                         | Minimum noise figure data              | No                        |

|              | Equivalent Noise<br>Temperature | TE                            | Equivalent Noise<br>Temperature data   | Yes <sup>1, 2</sup>       |

1. The port field of the NF/TE noise parameter must not be blank. If the port field *set NF/TE type* is blank, the following error message appears:

Error: in "Output xxxx"

Blank output node name for NF specified.

2. The port name of the NF/TE parameter must be consistent with the port name of the 2-port output.

The port name of the NF/TE output noise must be equal to one of the port names of the 2-port output; otherwise, the following error message appears:

Error: in "Output xxxx"

Port "xx" is not consistent with the 2-port specification node: "xx" or "xx"

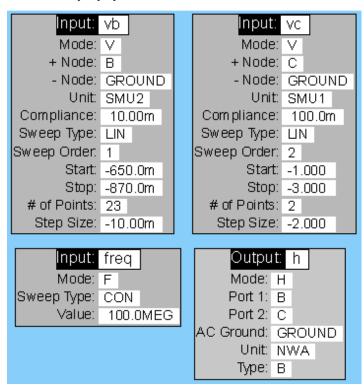

The following figure shows an example of input and output specifications for an H21-parameter *versus Vbe* setup.

Figure: Example Input and Output, 2-Port Simulation

#### Active Setup: /pnp/ac/h21vsvbe

Figure: Example Input and Output, 2-Port Noise Simulation

#### Active Setup: /bjt\_ncehf/sp/sparm\_noise\_bias

#### **2-Port Circuits**

An L-network of LCR is added to port 1 and port 2 to uncouple an AC signal from a DC bias to simulate a DUT using AC analysis. To see an actual input circuit deck, use the

# Simulator Debugger.

When the port 1 has an AC source, its signal goes through an R whose value is defined by TWOPORT Z0 and its default is 50 [ohm]. Then this signal is given to a port 1 through a C whose value is defined by TWOPORT C, and its default is 100 [F]. The port 1 is also connected to a DC bias source through an L whose value is defined by TWOPORT\_L and its default is 100 [H]. The port 2 has a similar L-network whose AC source is replaced by a short to ground.

#### 1 Note

As the default C and L values are so large compared to actual DUT values, sometimes it is necessary to specify smaller values to reduce numeric errors in simulation. For example, 1mF for C and 1mH for L are more realistic values.

There are two circuits in a single deck to represent two cases where the port 1 has a source and the port 2 has a source. These circuits are generated and added to a DUT for simulators.

# **Multiport Simulation**

Multiport simulations are currently only supported with the ADS simulator (hpeesofsim). This simulation type allows for 3 and 4 port S parameter simulations.

The following table describes the input and output specifications required for a valid setup for multiport simulation in ADS.

| INPUT MODE | VALID SWEEPS              | VALID OUTPUTS | <b>FOOTNOTES</b> |

|------------|---------------------------|---------------|------------------|

| F          | LIN, LOG, LIST, CON       | M             | 1, 2, 3          |

| V          | LIN, LOG, LIST, SYNC, CON | M             | 1, 2, 3          |

| I          | LIN, LOG, LIST, SYNC, CON | M             | 1, 2, 3          |

- 1. Exactly one frequency sweep required.

- 2. Exactly one multiport output M required.

- 3. **# of Ports** can be 3 or 4.

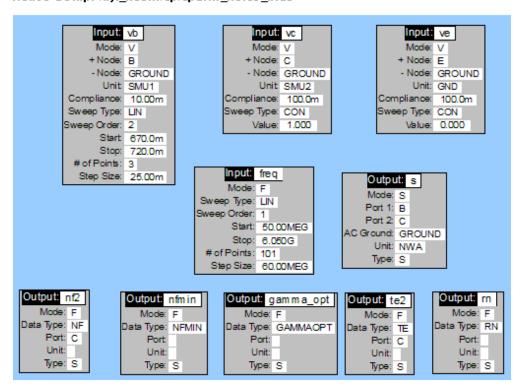

The following figure shows an example of input and output specifications.

Figure: Example Input and Output, Multiport Simulation

#### Simulation

#### MultiPortSparSimul\_Test.mdl Active Setup: /port3/Spar\_MultiPort/Spar\_MultiPort

#### **TDR Simulation**

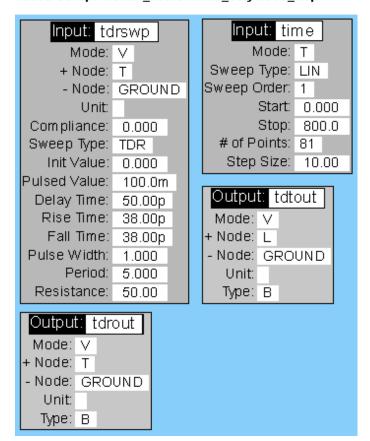

The following table describes the input and output specifications required for a valid setup for TDR (Time Domain Reflect) simulation.

| INPUT MODE | VALID SWEEPS                      | VALID OUTPUTS | COMMENTS |

|------------|-----------------------------------|---------------|----------|

| Т          | LIN, LIST, CON                    | V             | 1, 2, 3  |

| V          | LIN, LOG,L IST, SYNC, CON,<br>TDR | V             | 1, 2, 3  |

| I          | LIN, LOG, LIST, SYNC, CON         | V             | 1, 2, 3  |

- 1. Exactly one time sweep required.

- 2. Only voltage outputs allowed.

- 3. Exactly one voltage sweep of type TDR required.

The following figure shows an example of input and output specifications for simulating the reflected and transmitted signal of a simple TDR circuit.

Figure: Example of Input and Output Specifications for a TDR Simulation

Active Setup: /noise/\_demo/noise\_nalysis/rb\_swp

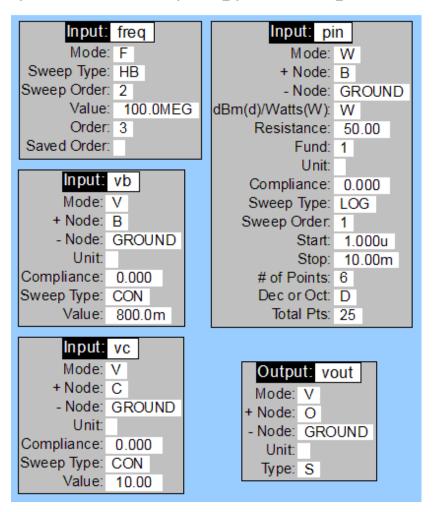

### **Harmonic Balance Simulation**

The following table describes the input and output specifications required for a valid setup for Harmonic Balance simulation.

| INPUT MODE | VALID SWEEPS                     | VALID OUTPUTS | COMMENTS      |

|------------|----------------------------------|---------------|---------------|

| V          | LIN, LOG, LIST, SYNC, CON,<br>AC | V, I          | 1, 2, 3, 4    |

| I          | LIN, LOG, LIST, SYNC, CON,<br>AC | V, I          | 1, 2, 3, 4    |

| F          | НВ                               | V, I          | 1, 2, 3, 4, 5 |

| W (Power)  | LIN, LOG, LIST, CON              | V, I          | 1, 2, 3, 4    |

- 1. Exactly one frequency sweep with Sweep Type = HB required.

- 2. Exactly one AC source required: V or I (AC), or W.

- 3. The Test Circuit includes elements such as DCFEED or DCBLOCK.

- 4. Units for the Power (W) source can be set to dBm(d) or Watts (W).

- 5. HB Sweep Type provides 3 fields, **Value:** the fundamental, **Order:** number of harmonics, and **Saved Order:** if blank, DC and all harmonics (that is, Order+1) is read back from simulator. Setting this to a lower value (N) reads only DC and the first N harmonics.

The following figure shows an example of input and output specifications for a BJT power-in versus power-out setup.

Figure: Example of Input and Output Specifications for a Harmonic Balance Simulation

hpsimvbic.mdl Active Setup: /vbic\_npn/hb/Harmonic\_Balance hpsimvbic.mdl Active Setup: /vbic\_npn/hb/Harmonic\_Balance

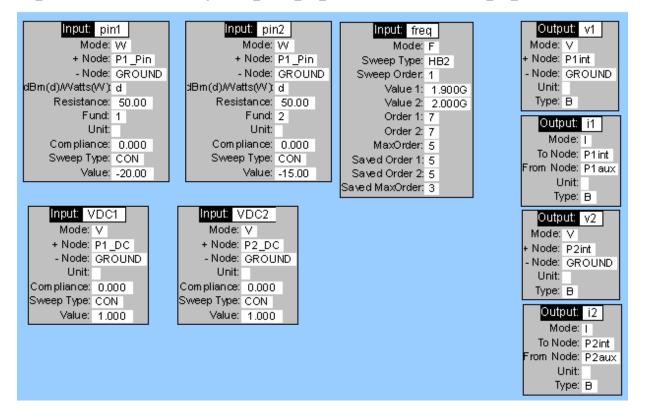

#### 2 tone Harmonic Balance

The 2 tone Harmonic Balance is currently only supported with the ADS simulator hpeesofsim. The following table describes the input and output specifications required for a valid setup for 2 tone Harmonic Balance simulation.

| INPUT MODE | VALID SWEEPS                        | VALID OUTPUTS | COMMENTS   |

|------------|-------------------------------------|---------------|------------|

| V          | LIN, LOG, LIST, SYNC, CON           | V, I          |            |

| I          | LIN, LOG, LIST, SYNC, CON           | V, I          |            |

| F          | HB2                                 | V, I          | 1, 6       |

| W (Power)  | LIN, LOG, LIST, CON, SYNC,<br>LSYNC | V, I          | 2, 3, 4, 5 |

- 1. Exactly one frequency sweep with Sweep Type = HB2 required.

- 2. Two Power sources with type W required, the setting field should be equal in these two sources.

- 3. Two Power sources can be in nested sweeps, master-sync or master-lsync pairs.

- 4. The Test Circuit includes elements such as DCFEED or DCBLOCK.

- 5. Units for the Power (W) source can be set to dBm(d) or Watts (W).

- 6. HB2 Sweep Type provides 8 fields.

- Value 1: the fundamental for the first tone

- Value 2: the fundamental for the second tone

- Order 1: number of harmonics of the first tone

- Order 2: number of harmonics of the second tone

- Saved Order 1: if blank, DC and all harmonics (that is, Order1+1) is read back from simulator. Setting this to a lower value (N) reads only DC and the first N harmonics.

- Saved Order 2: if blank, DC and all harmonics (that is, Order2+1) is read back from simulator. Setting this to a lower value (N) reads only DC and the first N harmonics.

- maxOrder: determines how many mixing products are to be included in a 2 tone simulation

- **Saved maxOrder:** if blank, all mixing products specified in maxOrder is read back from simulator. Setting this to a lower value (N) reads first N mix products.

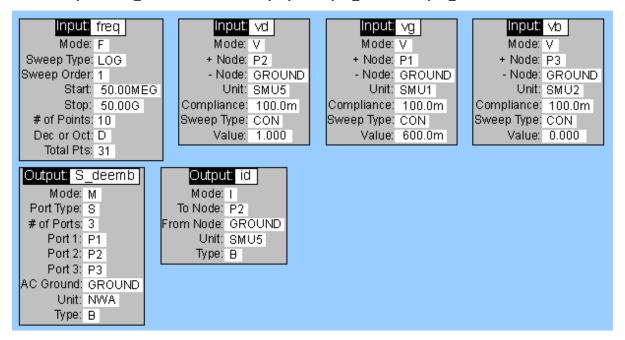

The following figure shows an example of input and output specifications.

Figure: Example of Input and Output Specifications for a 2 tone Harmonic Balance Simulation

#### HB MultiTone.mdl Active Setup: /ADS 2tone HB simulations/HB2/TwoTone HB demo

# **Performing a Simulation**

The steps to perform a simulation include:

- 1. Selecting a Simulator

- 2. Specifying Inputs and Outputs

- 3. Connecting Nodes

- 4. Specifying Parameter, Variable or Text Sweeps

- 5. Running a Simulation

- 6. Aborting a Simulation

# **Selecting a Simulator**

This section describes how you can set a simulator to begin with IC-CAP simulation.

The simulator can be set in one of the following three ways:

- Specify a default startup simulator

- Specify a simulator for a specific model, DUT, or setup

- Specify a simulator using a command

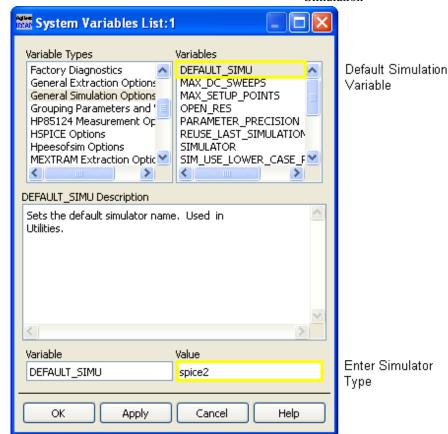

# **Default Startup Simulator**

You can specify a simulator as the default simulator on startup by setting the <code>DEFAULT\_SIMU</code> variable to one of the simulators. This setting is only effective if set at the global level. It is overridden if a different simulator is specified by setting a <code>SIMULATOR</code> variable or selecting a simulator through the <code>Select Simulator</code> command. When you exit the program, the <code>DEFAULT\_SIMU</code> setting is saved in the <code>.icconfig</code> file.

If this variable is not defined, the default simulator on startup is **spice2**.

# To specify a default startup simulator:

- 1. In the IC-CAP/Main window, select **Tools** > **System Variables**.

- 2. In the IC-CAP System Variables window, click **System Variables**.

- 3. In the System Variables dialog box, select **General Simulation Options** as the Variable Type and select the **DEFAULT\_SIMU** variable.

- 4. Enter the simulator name in the **Value** field and click **OK**.

**1** Note

4.

You can type the variable name and value in the System Variables window directly without going through the dialog box.

# Simulator for a Specific Model, DUT, or Setup

Some models require or perform better with a specific simulator. In these model files, you can specify a simulator for a model, DUT, or setup by setting the SIMULATOR variable. This allows you to use different simulators for different models, DUTs or setups, since a SIMULATOR variable can be specified at any level.

The following table lists the model files for which the SIMULATOR variable is defined.

**Table: Model Files with Predefined Simulators**

| Model File Name    | SIMULATOR Value |  |

|--------------------|-----------------|--|

| bjt_ft.mdl         | hpspice         |  |

| bjt_ncehf.mdl      | hpspice         |  |

| hpsimbjt_ncehf.mdl | hpeesofsim      |  |

| hpsimbjt_nhf.mdl   | hpeesofsim      |  |

| hpsimnpn.mdf       | hpeesofsim      |  |

| hpsimvbic.mdl      | hpeesofsim      |  |

| mxt504_npn.mdl     | hpeesofsim      |  |

| sabernpn.mdl       | saber           |  |

| spectre_ncehf.mdl  | spectre         |  |

| spectrenpn                  | spectre    |

|-----------------------------|------------|

| pn_diode.mdl                | spice2     |

| CGaas1.mdl                  | hpspice    |

| CGaas2.mdl                  | hpspice    |

| CGaashf.mdl                 | hpspice    |

| CGaashfax.mdl               | hpspice    |

| hpsimHPEEfet3.mdl           | hpeesofsim |

| UCBGaas.mdl                 | spice3     |

| UGaashf                     | spice3     |

| lc.mdl                      | spice3     |

| sabercirc.mdl               | saber      |

| sys110_verify.mdl           | hpspice    |

| hnmos6.mdl                  | hspice     |

| hnmos28.mdl                 | hspice     |

| hpmos28.mdl                 | hspice     |

| sabernmos.mdl               | saber      |

| noise_simu.mdl              | spice3     |

| bjt_1f_noise.mdl            | hpspice    |

| mos_1f_noise.mdl            | spice3     |

| opamp.mdl                   | hpspice    |

| bjt_ncehfp.mdl              | hpspice    |

| BSIM3_DC_CV_Measure.mdl     | spice3     |

| BSIM3_DC_CV_Extract.mdl     | spice3     |

| BSIM3_RF_Measure.mdl        | spice3     |

| BSIM3_RF_Extract.mdl        | spice3     |

| BSIM3_AC_Noise_Tutorial.mdl | spice3     |

| BSIM3_CV_Tutorial.mdl       | spice3     |

| BSIM3_DC_Tutorial.mdl       | spice3     |

| BSIM3_Temp_Tutorial.mdl     | spice3     |

| BSIM3_DC_CV_Finetune.mdl    | spice3     |

| BSIM4_DC_CV_Measure.mdl     | spice3     |

| BSIM4_DC_CV_Extract.mdl     | spice3     |

| BSIM4_RF_Measure.mdl        | spice3     |

| BSIM4_RF_Extract.mdl        | spice3     |

| BSIM4_DC_CV_Tutorial.mdl    | spice3     |

| BSIM4_DC_CV_Finetune.mdl    | spice3     |

|                             | 1 70 010 1 |

When a simulation is performed, IC-CAP looks for the SIMULATOR variable first, and if found, IC-CAP makes simulator specified in the variable as the active simulator.

The Select Simulator dialog box changes to reflect the name of the active simulator. If the SIMULATOR variable is not defined, IC-CAP uses the simulator displayed in the Select Simulator dialog box. For information on selecting a simulator using Select Simulator dialog box, refer to Specify Simulator Using a Command.

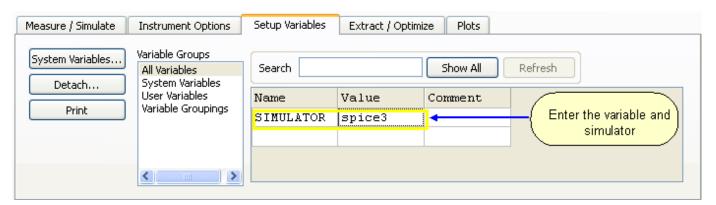

# To set a simulator for a specific model, DUT, or setup:

- 1. Select the appropriate model, DUT, or setup folder and click the corresponding **Variables** tab.

- 2. Type SIMULATOR in an empty variable **Name** field and type the name of the simulator in the corresponding **Value** field.

1 Note

To use a different simulator after one has been specified by the SIMULATOR variable, reset the simulator using the **Select Simulator** command.

# **Simulator Using a Command**

The **Select Simulator** command sets the simulator to be used for all simulations performed in the current session, except when simulating a model, DUT, or setup for which a SIMULATOR variable has been defined.

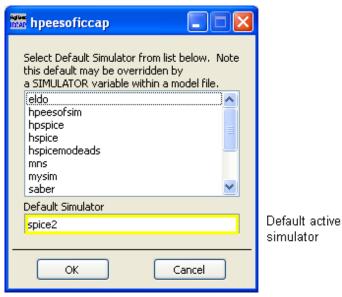

# To set a simulator without using a variable:

1. In the IC-CAP Main window, choose **Tools > Select Simulator**. A hpeesoficcap dialog box is displayed which list the supported simulators.

2. Select a simulator name or type the name of a simulator you have linked with IC-CAP in the **Default Simulator** field and click **OK**.

# **Specifying Inputs and Outputs**

When running a simulation, IC-CAP builds the simulation input deck using the circuit description and the input and output specifications. The circuit description provides the model information. The input and output specifications provide the input stimuli and requested output data, as well as the information needed to determine the type of simulation being performed.

Specifying inputs and outputs is independent of the type of simulation being performed. When specifying input for a simulation, you must enter the sweep mode in the **Mode** field of the Input table, and the node connections. The **Input** field changes, depending on the type of mode specified.

# **Connecting Nodes**

The convention used for node connections when sourcing voltage and current are provided below:

- When you specify an Input Mode of V, the +Node and \*-Node\* fields are available in the Input table. In this case, the +Node is considered to be the positive side of the voltage source and the -Node is the negative side.

- When you specify an Input Mode of *I*, the **To Node** and **From Node** fields are available in the Input table. Current flows from the **From Node** to the **To Node**.

When IC-CAP builds the simulation input deck, it creates the source name by concatenating the mode character, the first three characters of the **+Node (or To Node)** and the first three characters of the **-Node (or From Node)**. These source names are used in the simulation input deck to specify the sweeps and constants. Specified outputs may also reference these names.

Source names are limited to 8-characters. This limit may cause issues in a simulation, if, for example, two inputs are specified as follows:

| Mode = V        | Mode = V         |

|-----------------|------------------|

| +Node = BASE    | +Node = BASE     |

| -Node = EMITTER | -Node = EMITTER2 |

From this input, IC-CAP creates the same source names: VBASEMI and VBASEMI. You can

avoid this potential conflict with source names by choosing node names in circuit descriptions carefully. When choosing node names with more than three characters, make sure that the first three characters are unique with respect to the first three characters of any other node names.

When you enter an invalid node name, such as K in any of the input and output node fields and try to simulate, the program sends an error message:

ERROR: Invalid Input node name K used

ERROR: Unable to simulate.

Check the Input and Output specifications.

# **Specifying Parameter, Variable or Text Sweeps**

In addition to the list of valid sweep modes for each simulation type listed, you can sweep parameter values and variables. For example, you can generate a family of beta versus IC curves by using the BF parameter of the bipolar transistor model as the step input or you can sweep the operating temperature variable TEMP to analyze temperature effects.

# **0** Note

You can set the value for a constant or values for sweeps of the simulation temperature by adding the TEMP variable to the variable table and creating an input (Mode = Parameter and Name = TEMP) in the setup.

# To sweep parameters or variables:

- 1. In the Model window, select the DUT and the setup.

- 2. Click Measure/Simulate.

- 3. Click **New Input**. The Input Editor is displayed.

- 4. In the **Mode** field, select **Parameter** from the drop-down list.

- 5. Specify a parameter or variable by entering its name in the **Param Name** field.

- 6. Enter all other necessary information and click **OK**.

A parameter sweep is a valid input mode for all simulation types. Specifying parameter

#### Simulation

sweeps may differ for devices and circuits depending on the type of simulator being used.

For an example of simulator-specific parameter sweeps, refer to the following topics:

- SPICE Parameter Sweeps (simulation)

- Saber Parameter Sweeps (simulation)

- ADS Parameter Sweeps (simulation)

# **Hierarchical Parameter Sweeps**

You can perform parameter sweeps when using hierarchical models. However, when you sweep a parameter from a model lower than the level from which the simulation is being performed, you must specify the complete path name of the parameter in the Name field of the input.

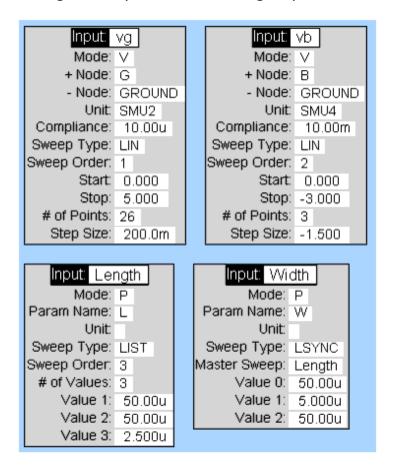

# **Sychronized List Sweeps (LSYNC)**

To synchronize a parameter sweep with other parameter sweeps, set the sweep type to LSYNC ( *Synchronized List* when using the *Edit* feature on an input). Just like a normal SYNC sweep, you must specify the name of the master sweep by entering it in the *Master Sweep* field.

Unlike a normal SYNC sweep, the entries are not limited to an offset and a multiplier. The LSYNC sweep enables you to specify an arbitrary list of points. IC-CAP automatically provides the required number of points after the master sweep is set. If the number of points in the master sweep changes, simply click on the LSYNC *Master Sweep* field to update the number of points in the input.

One application of LSYNC sweeps is to simulate an arbitrary collection of device Lengths and Widths.

If a master sweep and multiple LSYNC sweeps are saved to an MDM file, they can only be imported into a setup where the same sweeps are either all CON sweeps or the sweeps are synchronized using LSYNC. One sweep cannot be a LIN sweep and another one be a CON sweep, even if that combination exist in the MDM file. To use a LIN sweep with a CON sweep, use LSYNC to synchronize the CON sweep to the LIN sweep and enter the same value for all list points.

The LSYNC sweep type is only available with Parameter sweeps. The LSYNC sweep is not supported with the Saber simulator.

# **Specifying Text Sweeps**

The sweep type TLIST is a LIST accept string values. The sweep type TLSYNC is LSYNC accept string values.

# **0** Note

These two sweep types are only available with Parameter sweeps.

The system variable RETAIN\_DATA is used for keeping the data when changing the sweep type.

# **Simulating Open Circuits**

IC-CAP uses the OPEN\_RES variable to handle any floating nodes. This variable allows an open circuit to be simulated as a large resistance. The value of the resistance is equal to the value of the OPEN\_RES variable. A resistor of this magnitude is automatically connected to all external circuit nodes not connected to a specified source. When the OPEN\_RES variable is not specified, a current source set to zero (0) amps is used instead. However, using the current source may cause simulation convergence problems.

# **Running a Simulation**

You can perform a simulation on an active setup or on all the setups in an active DUT.

#### **Simulating an Active Setup**

To perform a simulation on the active setup, select the setup and click **Simulate Setup** icon ( ) in the Model window.

You can also choose **Simulate > Active Setup** from the menu bar of the Model window to perform simulation on an active setup.

Simulating All the Active Setups in a DUT

To perform a simulation on all the setups in an active DUT, select the DUT and choose **Active DUT** under **Simulate** menu in the Model window.

# **Aborting a Simulation**

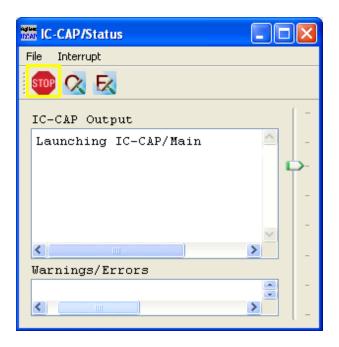

You can abort a running simulation at any time from the IC-CAP Status window.

#### To abort a simulation:

Click Interrupt IC-CAP Activity icon or choose **Interrupt > IC-CAP Activity** in the IC-CAP/Status window.

After you abort a running simulation, the simulation stops and the following message appears in the Status window:

HALTED: Simulation interrupted by user

# **Using Simulation Debugger**

The Simulation Debugger is a useful tool for determining why a simulation failed.

When a simulation fails, the program displays an error message:

Simulation Failed: Data Unchanged Use Simulation Debugger in Utilities Menu for more information

The SPICE-type simulators accept an input deck that contains both the circuit description and analysis commands.

The Saber simulator requires two separate decks. The Saber input deck, displayed in the Input editor, contains the circuit description, written in the MAST modeling language. The Saber command deck, displayed in the Command editor, contains the analysis commands to be performed by the simulator. The Command editor is only used with the Saber simulator.

The input editor displays the input information used in the simulation. For Saber simulations, the command editor information is used also. You can quickly see how changes would affect your results by changing the input (and for Saber, command) files, performing a manual simulation, and observing the results in the output editor. For more information, refer to <u>Using the Manual Simulate Function</u>.

In many cases, the output text file includes the error messages displayed when the simulation fails. You cannot edit an output text file.

# To use the Simulation Debugger:

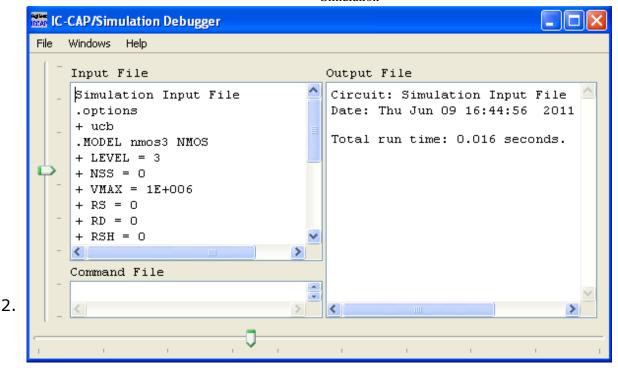

- 1. In the IC-CAP/Main window, click **Simulation Debugger** icon ( ). The IC-CAP Simulation Debugger window is displayed. By default, the Input, Command, and Output editors are blank.

- 2. Initiate the simulation in the Model window. The program sends the input deck and output text files to the input and output editors of the Simulation Debugger.

#### Simulation

### **Manual Simulate Function**

The **Manual Simulate** function simulates the input deck displayed in the **Input Editor**. For example, you can perform a manual simulation after changing some parameter values or sweep values directly in the input file deck, without having to change these values in the IC-CAP Circuit definition, parameter tables, or input and output specifications.

#### To execute a manual simulation:

1. In the Simulation Debugger window, edit the inputs and command decks displayed in the Input and Command editors panes.

```

Input File

Simulation Input File

.options

+ ucb

.MODEL nmos3 NMOS

+ TEAET = 3

+ UO = 2000

+ VTO = 1.136

+ NFS = 1E+012

+ TOX = 1E-007

+ NSUB = 5.31E+015

+ NSS = 1

+ VMAX = 1E+006

+ RS = 0

+ RD = 0

+ RSH = 0

<

```

2. Then, select **File > Manual Simulation** in the Simulation Debugger window.

# **Saving the Simulation Debugger Files**

You can save the input, command, and output files displayed in the individual panes of the Simulation Debugger.

# To save Simulation Debugger Input, Output, and Command files:

Select File > Save and choose the appropriate option in the Simulation Debugger window.

2. In the Input Prompt dialog box, enter a file name.

If you enter a file name only, the file is saved to the current working directory. To save the file to another directory, enter the file name along with the full path.

# Linking a Simulator to IC-CAP

The interface for linking a simulator to IC-CAP depends on the type of simulator being used.

A non-piped simulation receives the input deck information from a file, performs the simulation, and sends the binary output data and resulting text output to other files. The simulator process is restarted for every simulation. The non-piped simulations are identical, regardless of simulator type.

The definition of a piped simulation differs for SPICE simulators, Saber simulators, and the ADS simulator. For descriptions of these differences, refer to one of the following:

- Piped and Non-Piped SPICE Simulations (simulation)

- Piped and Non-Piped SPECTRE Simulations (simulation)

- Piped and Non-Piped Saber Simulations (simulation)

- Piped ADS Simulations (simulation) and Non-Piped ADS Simulations (simulation)

The following simulator links have been tested to work for IC-CAP 2002 PC:

- Remote to spectre on UNIX

- Local to HSPICE on PC

- Local to hpeesofsim on PC

- Local to SPICE2 on PC

- Local to SPICE3 on PC

- Local to HPSPICE on PC

The following simulator links may work for IC-CAP 2002 PC, but were not thoroughly tested:

- Remote to HSPICE on UNIX

- Remote to HSPICE on another PC

- Remote to hpeesofsim in CANNOT\_PIPE mode on another PC

- Remote to hpeesofsim in CANNOT\_PIPE mode on UNIX

# **Adding a Simulator**

The IC-CAP Open Simulator Interface allows the addition of any simulator to IC-CAP. The <u>Figure: IC-CAP Open Simulator Interface Data Flow Diagram</u> shows a data flow diagram of this interface.

In this design, the IC-CAP system has no knowledge of your simulator. The circuit description is entered in the format corresponding to the template name in the usersimulators field (second argument).

| Template Name     | Syntax           |

|-------------------|------------------|

| spice2            | spice            |

| spice3            |                  |

| hpspice           |                  |

| hspice            |                  |

| eldo              |                  |

| spectre443        |                  |

| spicemodeads      |                  |

| spectre spmodeads | spectre          |

| saber             | saber            |

| hpeesofsim        | hpeesofsim (ADS) |

These simulators are referred to as the *template* simulators when writing interface code. For example, when you specify a circuit description with syntax matching the syntax of *spice2*, then *spice2* is referred to as the *template* simulator.

**IC-CAP Open Simulator Interface Data Flow Diagram**

IC-CAP generates the input deck as if the selected simulator were the template simulator. When you enter your simulator in the *Select Simulator* dialog box or the SIMULATOR variable, the input deck is sent through a module of code that you have written. This module of code is referred to as the *Translation Module* in the figure. The Translation Module consists of two translators. The first translates the IC-CAP generated input deck to your simulator's input deck. The deck is then sent to your simulator for analysis. When the simulation is completed, the second translation accepts your simulator's raw data and converts this to the raw data format of the template simulator. This data is returned to IC-CAP for evaluation.

Starting with IC-CAP 2002 PC and IC-CAP 2004 UNIX, you can specify whether the simulator returns the raw data in big-endian or little-endian format. If you do not specify a format, IC-CAP assumes that the data is returned in the order native to the platform, which is big endian for UNIX and little endian for the PC. To specify big endian, append .be or the alias .hpux or .sparc to the template name. To specify little endian, append .le or the alias .pc to the template name. For additional information, see the *README.byteorder* file in the source directory \$ICCAP\_ROOT/src directory.

It is possible to have a circuit description in the native syntax of the simulator that you will use. This is done by using the Open Circuit Parsing Interface that is available in IC-CAP. Though the netlist body is provided in your selected simulator's native syntax, the source and sweep information that IC-CAP adds to the netlist body is still in the template syntax. To use this interface, you must specify the name of the executable responsible for

generating the netlist body.

When the Simulation Debugger is running, the file displayed as the input file is the template simulator's input deck generated by IC-CAP. The Simulation Debugger's output file can be any text file generated in the Translation Module section of code. This allows many options with respect to what information can be included in this text file that may be helpful for debugging purposes.

The Translation Module section of code consists of the two translators, but may also include any other desired functionality. For example, you may read the text file back from your simulator and send this file back to IC-CAP to be displayed in the Simulation Debugger's output file. The Translation Module can also be written to generate debug statements in a text file to show the progress of the input and output translations. This text file can then be sent to IC-CAP and displayed in the Simulation Debugger's output file.

As part of the interface code, you are supplied with a file called *usersimulators* in the directory \$ICCAP\_ROOT\iccap\lib. This file must contain the user-specified information for each simulator added to the IC-CAP system. Five fields of information must be specified when adding a user simulator to IC-CAP. The fields of information must be separated by a space. The fields may or may not be surrounded by quotation marks. A blank, such as *host\_name*, is indicated by a pair of quotation marks (""). An optional sixth field is available to use the Open Circuit Parsing Interface.

# The general format is as follows:

```

simulator_name template_name path_name host_name pipe_capability

[parser path] [special path]

```

### where:

simulator\_name is the name of the user simulator being added to the list. This is the name you will specify when selecting the simulator in the Select Simulator dialog box or the SIMULATOR variable. You may assign any name to this field EXCEPT for any of the reserved IC-CAP template names. The reserved template names are shown in the table IC-CAP Supported Simulators and Corresponding Template Names (simulation).

template\_name is the name of the template simulator. The user-written translation modules map the input file format of the user's simulator to the input file format of the template simulator. Likewise, the output file format of the template simulator is translated into the output file format of the user's simulator. To specify that the simulator returns the raw data in big endian format, append .be or the alias .hpux or .sparc. To specify that the simulator returns the raw data in little endian format, append .le or the alias .pc.

path\_name is the complete path name of the user's simulator executable file or translation module. Use back slashes when naming the path to a simulator on a PC and forward slashes when naming the path to a simulator on UNIX.

host\_name is the host machine name on which the simulator can be used. The

purpose of this information is for remote simulations where only a particular computer is able to access a simulator. If this field is blank, indicated by a pair of quotation marks (""), the simulation is executed on the machine currently running IC-CAP. The format of host name is  $< host > [< tmp \ dir >]$ , where <host> is any host name permitted by rsh and remsh. Examples include remotebox, remotebox.my.com, 192.168.4.4, and icuser@remotebox. The last form enables users with sufficient permission to simulate to the machine remotebox as if the user icuser was performing the simulation. This is useful when simulating to a UNIX machine from a PC when the login names for the PC don't match the login names for the UNIX machine. < temp dir > is optional and it enables you to specify a location for IC-CAP's temporary files. The default location is /var/tmp on the remote machine. For example, if a PC is running services and it meets the requirements in *Network Security* (simulation), /var/tmp (UNIX notation) may not work for the PC. You can override this by specifying something like \_c:\temp\_. For more information, see Remote Simulation (simulation).

pipe\_capability is either CAN\_PIPE or CANNOT\_PIPE. It specifies whether or not the simulator has the ability to perform piped simulations. When CANNOT\_PIPE is specified in this field, a non-piped simulation is done even when the IC-CAP simulation debugger is off.

parser\_path is an optional entry that specifies the name of the executable responsible for generating the netlist body and providing IC-CAP with the necessary parameter/node information.

special\_path is a simulator-specific field and may have different meanings for each simulator. Currently it is only required by the saber interface and will be ignored for any other simulator template. The field can be completely omitted from all templates but saber. For saber, it should provide the path to the aimsh executable in your saber installation. Note, to specify this field without declaring a parser\_path, you must specify two quotations "" for the parser\_path field.

# **Using the Open Circuit Parsing Interface**

To use the interface and generate a circuit description in the native syntax of the simulator, you must specify the executable in the *usersimulators* file. This optional field in *usersimulators* is the path to the circuit parser. This enables the simulator link to use your simulator's native syntax in IC-CAP's circuit description shown in the Circuit folder. Without this interface, your circuit must be represented as *spice*, *hpeesofsim*, or *sabre*. If you specify an executable, it is responsible for the following actions:

- Creates a parsed\_file that IC-CAP will use to merge parameters at each simulation.

- Identifies all pertinent parameters for in the DUT Parameters and Model Parameters folders.

- Identifies the number and names of all nodes that will be used in IC-CAP.

Your parser will be invoked with two arguments, the source file name and the output file name. The parser is responsible for generating the output file which is the same as the input file with substitutions for node names, parameters, and model names. In addition,

the circuit type must be declared.

Determining the circuit type differs depending on the template being used. For any of the *spice* templates, the netlist should consist of one instantiation of one model or a subcircuit.

```

<instance line>

<model card>{code}

or

.subckt

.

.ends

```

The first should be declared a circuittype of the first character of the instance line. The second should be declared a circuit of type X. The instance line should be omitted from the output file as IC-CAP will generate this line with the proper node numbers for the type of simulation being performed.

For hpeesofsim simulations, the circuit is similar, either a subcircuit, or a model and an instance. circuittype for a subcircuit is still X, but for the instance netlist, the type is always D.

For *saber* simulations, circuittype is again a *D* for device netlists and an X for subcircuit netlists, but for this template, you must set device type as well which is the actual name of the device type.

The output file should place the token \$ where the name of the model should appear in the netlist. It should place the token <name>\$ where the value for parameter named <name> should appear.

```

Example Device circuit:

D1 1 = A 2 = C DIODE

.MODEL DIODE D

+ IS = 1E-14

+ N = 1.0

+ BV = 1000

+ IBV = 1m

+ RS = 0

+ CJO = 0

+ VJ = 1.0

+ M = 0.5

+ FC = 0.5

+ TT = 0

+ EG = 1.110

+ XTI = 3.0

Output File:

.MODEL $modname$ D

+ IS = pvalIS

+ N = pvalN

+ BV = pvalBV

```

```

+ IBV = $pvalIBV$

+ RS = pvalRS

+ CJO = $pvalCJO$

+ VJ = pvalVJ

+ M = pvalM

+ FC = $pvalFC$

+ TT = $pvalTT$

+ EG = $pvalEG$

+ XTI = $pvalXTI$

Example subcircuit circuit

.OPTION gmin=1e-30

.SUBCKT LED 1=A 2=C

RS 1 11 1m

DLO 11 2 DLO

DHI 11 2 DHI

.MODEL DLO D

+ IS = 1E-29

+ N = 1

.MODEL DHI D

+ IS = 1E-34

+ N = 1

+ CJO = 100p

+ M = .4

+ \vee J = 2

+ FC = .5

.ENDS

Output File:

.SUBCKT $modname$ 1 2

RS 1 11 $pvalRS$

DLO 11 2

+ DLO

DHI 11 2

+ DHI

.MODEL DLO D

+ IS = $pvalDLO.IS$

+ N = pvalDLO.N

.MODEL DHI D

+ IS = $pvalDLO.IS$

+ N = pvalDLO.N

+ CJO = $pvalDLO.CJO$

+ M = pvalDLO.M

+ VJ = $pvalDLO.VJ$

+ FC = $pvalDLO.FC$

.ENDS

```

The parser must print the commands to standard output that tell IC-CAP about the circuit it has parsed. Each line must meet one of the following formats:

PARAM <name> <value>

MODELPARAM < name > < value >

DEVPARAM < name > < value >

DEVMODELPARAM < name > < value >

DEVPARAMs and DEVMODELPARAMs are parameters that are to appear at the DUT level. The difference between DEVPARAMs and DEVMODELPARAMs are that

DEVMODELPARAMs appear in model cards.

MODELPARAMs are PARAMs that appear in model cards. PARAMs and MODELPARAMs appear in the model parameters page.

<name> is the name of the model. <value> is its default value. For certain saber parameters that can be altered, you may prepend SPECIAL to any of the PARAM keywords.

### NODE < nodename >

Each NODE line declares a node to be recognized in IC-CAP setups. The order of the NODE lines must match the order the nodes are to appear when IC-CAP instantiates the instance card.

#### CIRCUITTYPE <x>

Here  $\langle x \rangle$  is a single character. See above discussion of circuit types for proper values.

### DEVICETYPE <x>

Here  $\langle x \rangle$  is the name of the device for a device type circuit. See discussion about circuit types. This line is only required for saber.

#### UNRESOLVED <x>

Here <x> is the name of a model which was referenced in the netlist, but had no associated model card. In this case IC-CAP will try to find a model in its loaded list of models to insert.

### ERROR: <x>

Here  $\langle x \rangle$  is any arbitrary error message. The space after the colon is required. The entire line, including ERROR: will be reported in an error dialog.

#### DECKCOMPLETE

This should be the last line issued indicating that the parse is successful and that the output file is generated.

# **Translation Module Example**

An example translation module, \$ICCAP\_ROOT/src/mysim.c, is provided with IC-CAP. The executable version of this program is \$ICCAP\_ROOT/bin/mysim. The following line is an example for adding a simulator called mysim to the IC-CAP simulator list:

```

mysim spice2 $ICCAP_ROOT/bin/mysim "" CAN_PIPE

```

### where:

The simulator *mysim* uses *spice2* as the template simulator. *mysim* is a user-written module that does the following:

- Translates a *spice2* input format deck to a *mysim* input format deck.

- Makes the call to the user's simulator. In this example, the executable simulator is *spice2*.

- Translates the user's binary output format to *spice2* binary output format.

- Optionally sends information to the output text file.

mysim is located in the \$ICCAP\_ROOT/bin directory.

The current host computer can perform a *mysim* simulation. The quotation marks ("") mean that no remote host is specified and therefore the simulation can be done on the current host machine.

The simulator *mysim* is capable of piped simulations.

After creating a translation module, you must compile it, using the system command:

cc -o mysim mysim.o -lm

### **0** Note

Whenever \$ICCAP\_ROOT/iccap/lib/usersimulators is modified, always restart IC-CAP to read the new simulator configuration. This file may be a symbolic link on SunOS so that each host served by a single file server can have a different simulator configuration.

#### **Reserved Simulator Names**

The following simulator names are reserved by IC-CAP and you cannot assign the same name to a different simulator:

spice2, spice3, hpspice

The following simulator names are defined in the *usersimulators* file but you can change their name and assign the same name to a different simulator.

hspice, saber, eldo, precise, spectre, spectre spi, pspice, hpeesofsim

### **Simulator Argument Syntax**

The command syntax for each simulator differs depending on whether a piped or non-piped simulation is being invoked. For details, refer to the documentation for each simulator (ADS Simulator (simulation), Saber Simulator (simulation), SPICE Simulators (simulation)).

# **Remote Simulation**

You can perform a simulation on a computer other than your computer by using the remote simulation feature. You can perform remote simulation due to any of the following reasons:

- Running the simulation on a faster machine

- Running the simulation on a computer authorized to run a particular simulator

- Running the simulation with a simulator that is not supported on the machine running IC-CAP, but supported on a remote machine

# **Before you Begin with Remote Simulation**

To execute a remote simulation, the remote machine must meet the following requirements:

• The remote machine must possess Linux, SunOS, or a similar operating system that supports execution of Berkeley's remote shell (remsh or rsh) and remote file copy (rcp) commands. Alternatively, if the machine supports secure shell (ssh) and secure shell copy (scp), IC-CAP can be configured to this mechanism by modifying iccap.cfg file.

### **1** Note

The remote machine must be set to receive secure shell connections. The machine running IC-CAP must have ssh and scp installed for this mechanism to function.

- Both local and remote machines are familiar with each other. This means that both the machines are connected through a network and the IP address database is updated to respond to the other machine. This database is usually found in /etc/hosts.

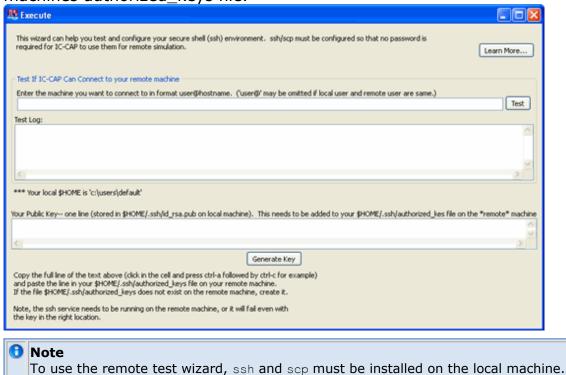

- Allows remote shell and copy program execution from your local host without entering a password (relaxed network security). With ssh/scp, this requires generation of an authentication key. A utility is provided at \$ICCAP\_ROOT/examples/model\_files/misc/Setup\_SSH.mdl to assist with the generation of the key.

- Allows for the removal of files using /bin/rm.

- The remote machine must contain /var/tmp directory to write temporary files unless an alternate directory is specified in the usersimulators file for that simulators host\_name field. See host\_name (simulation) for more information.

The procedure for setting up the appropriate network security for your simulator depends on the remote host operating system.

# **Remote Simulation Algorithm**

The name of the remote host is specified in the usersimulators file under \$ICCAP ROOT/iccap/lib file path. Remote simulation is supported in both CAN PIPE and CANNOT PIPE mode for *most* simulators. However, few simulators may only work in CANNOT PIPE mode. See *Linking a Simulator to IC-CAP* (simulation).

The machine name for a simulator in the usersimulators file determines where each simulator runs.

- When a remote machine is not specified, the simulation occurs locally on your host computer.

- If the remote machine is specified, ensure that remote machine name is same as the current host name. When the remote machine is identical to the current host, the simulation is executed on the current host directly.

- If a remote machine is specified and remote machine name is not the same as the current host name, a remote simulation is performed by a remote shell command as shown below:

### For SunOS and Linux

/usr/ucb/rsh

#### On a PC

cygwin ssh

cygwin rsh can be configured in iccap.cfg file but for Windows XP only. The cygwin rsh shipped with IC-CAP does not function under Windows Vista or Windows 7.

• In non-piped simulation, necessary files are copied to the remote machine using a remote file copy command as shown below:

#### For SunOS and Linux

/usr/ucb/rcp

### On a PC

cygwin scp

cygwin rcp can be configured in iccap.cfg for Windows XP only. The cygwin rcp shipped with IC-CAP does not function with Windows Vista or Windows 7.

# **Network Security**

When the remote commands (listed in the <u>Remote Simulation Algorithm</u> are executed, the current user ID is used to establish access to the remote machine. Therefore, it is necessary to have the same user ID on both local and remote machines. Also, the following files must be modified to allow remote program execution from a particular host.

# For rsh/rcp

- /usr/adm/inetd.sec

- /etc/hosts.equiv

- . rhosts

# For ssh/scp

- . ssh/known hosts

- . ssh/authorized keys

# Reconfiguring IC-CAP to use ssh/scp or rsh/rcp

IC-CAP defaults to rsh/rcp on Linux or Sun and to ssh/scp on Windows operating system. Due to site security restrictions, it could be necessary to reconfigure IC-CAP on Linux or SunOS to use ssh/scp, or if you are using Windows XP, it could be appropriate to use rsh/rcp. To change the mechanism used by IC-CAP, you must modify the C\_REMOTE\_SH\_CMD and IC\_REMOTE\_CP\_CMD variables in your iccap.cfg file (for more details on configuring the iccap.cfg file, refer to Customization and Configuration (customization)).

The default values of C REMOTE SH CMD and IC REMOTE CP CMD variables are:

#### On Windows

```

IC_REMOTE_SH_CMD=%ICCAP_PC_UNIX_CMDS\ssh.exe

IC_REMOTE_CP_CMD=%ICCAP_PC_UNIX_CMDS\scp.exe

```

To change the default on Windows, use the following commands:

```

IC_REMOTE_SH_CMD=%ICCAP_PC_UNIX_CMDS\rsh.exe

IC_REMOTE_CP_CMD=%ICCAP_PC_UNIX_CMDS\rcp.exe

```

### On Linux

```

IC_REMOTE_SH_CMD=/usr/bin/rsh

IC REMOTE CP CMD=/usr/bin/rcp

```

#### On SunOS

```

IC_REMOTE_SH_CMD=/usr/ucb/rsh

IC REMOTE CP CMD=/usr/ucb/rcp

```

To change the default on Linux or SunOS, specify the full path to ssh and scp depending on your system installation.

# Validating rsh/rcp

When the security is set up, ensure that the following command returns the current date without any errors (substitute your remote machine name where < remote\_machine > appears in the example).

On SunOS or Linux, type:

```

rsh <remote_machine> date

```

For the PC, execute the following line of PEL in an IC-CAP macro. The results are displayed in the IC-CAP Status window.

```

print system$("rsh <remote machine> date")

```

# Validating ssh/scp

Perform the following steps to test remote simulation:

- 1. Open the Setup\_SSH.mdl example file from the examples/model\_files/misc directory. The ssh\_Config model file icon is displayed in the IC-CAP Main window.

- 2. Double-click the model icon to open the remote test wizard. The remote test wizard tests the ssh connection and and generates a key which can be copied to the remote machines authorized keys file.

This the recommended way to test remote simulation for Windows Vista and Windows 7.

# **Specifying the Remote simulator**

If your remote simulator requires licensing variables, write a small shell-script on the remote host machine. The shell-script sets all the required environment variables before invoking the simulator. The shell script is specified in your *usersimulators* file instead of the actual simulator executable.

### Example:

```

#!/bin/sh

LM_LICENSE_FILE=my_license_file.lic

export LM_LICENSE_FILE

PATH=/path/to/my/simulator/bin:$PATH

export PATH

/path/to/my/simulator/bin/xxxxx $*

```

The \$\* on the last line is required to pass along the IC-CAP command-line parameters.

# **Executing a Remote Simulation**

After the *usersimulators* file is set up correctly and the network security is adjusted, the

steps for performing a remote simulation are identical to those required to perform a nonremote simulation. For more information, refer to *Performing a Simulation* (simulation).

### **1** Note

Ensure that there are no commands in the .cshrc file on the remote host that may generate output. Also, do not perform terminal related operations in your .cshrc file such as termset or stty. Since there is no physical terminal with remote shell commands, commands expecting one in your .cshrc file lead to errors.

# **Remote Simulation Examples**

The following example specifications for running the template simulators remotely can be added to the usersimulators file in the \$ICCAP ROOT/iccap/lib filepath.

### 1 Note

If you prefer to preserve the defaults as shipped, you can add the specifications to your local, or Home, directory by copying and editing the usersimulators file. If you set the specifications in your home directory, you must change the pointers in your configuration file. Copy the file \$ICCAP ROOT/config/iccap.cfg to \$HOME/hpeesof/config/iccap.cfg. See Customization and Configuration (customization) for additional information.

The examples contain sample user-assigned simulator names, remote host machine names, and directory path (on the remote machine) information. This information must be replaced by the actual names in your system. The purpose of these examples is to show the names of the simulator executable files.

You must specify a full path name for each simulator because the PATH variable on the remote machine may not have the necessary search path to find your simulator.

#### 1 Note

User-assigned simulator names can be any name you choose except for the reserved names. See Reserved Simulator Names (simulation). To use a user-assigned simulator, ensure that the simulator name is listed in the first column of the usersimulators file, and then set your simulator in IC-CAP to the same name.

# **Running spectre on the Remote Solaris Machine**

To run spectre on the remote Solaris machine called *cadencebox*, enter the following command:

remspectre SS spectre443 /cadence/5.0.0/tools/bin/spectre "cadencebox" CANNOT PIPE

where,

spectre443 is the template for spectre version 4.4.3 and greater, which causes IC-CAP to parse its circuit page expecting spice syntax.

# Running spectre from a PC

From a PC, enter the following command:

remspectre\_SS spectre443.be /cadence/5.0.0/tools/bin/spectre "cadencebox" CANNOT PIPE

Since the Solaris machine's byte order is big endian, append the .be extension to the template name.

### Running Native spectre on the remote Solaris Machine

To run native spectre on the remote Solaris machine called *cadencebox*, enter the following command:

remspectre spectre /cadence/5.0.0/tools/bin/spectre "cadencebox" CANNOT PIPE

where,

spectre is the template for native spectre, which causes IC-CAP to parse its circuit page expecting native spectre syntax. See SPECTRE Interfaces (simulation).

### Running Native spectre from a PC

From a PC, enter the following command:

remspectre spectre.be /cadence/5.0.0/tools/bin/spectre "cadencebox" CANNOT\_PIPE

Since the Solaris machine's byte order is big endian, append the .be extension to the template name.

# Running UCB SPICE 2G.6 on a Remote Machine

To run UCB SPICE 2G.6 on the remote machine called *spice2mach*, enter the following command:

spice2rem spice2 /usr/iccap/bin/ucbspice2g6 "spice2mach" CAN\_PIPE

where:,

*spice2rem* represents the name of the simulator and *pipe* creates an interprocess channel that responds to read/write calls.

To run UCB SPICE 3E2 on the remote machine called *spice3mach*, enter the following command:

spice3rem spice3 /usr/iccap/bin/spice3e2 "spice3mach" CAN\_PIPE

where,

*spice3rem* represents the name of the simulator and *pipe* creates an interprocess channel that responds to read/write calls.

### Running HPSPICE on a Remote Machine

To run HPSPICE on the remote machine called *hpspicemach*, enter the following command:

hpspicerem hpspice /usr/iccap/bin/shpspice "hpspicemach" CAN PIPE

where,

*hpspicerem* represents the name of the simulator and *pipe* creates an interprocess channel that responds to read/write calls.

When performing remote simulations using the HPSPICE simulator, *both* of the executable files called shpspice and spice2.4n1 must be present on the remote machine.

To run HSPICE on the remote machine called *hspicemach*, enter the following command:

hspicerem hspice /usr/bin/hspice "hspicemach" CANNOT\_PIPE

where,

*hpspicerem* represents the name of the simulator and *pipe* creates an interprocess channel that responds to read/write calls

Depending on the version of HSPICE you have installed, the execution script called *hspice* can exist in a different directory path from /usr/bin/hspice. In this case, create a symbolic link from /usr/bin/hspice to the actual *hspice* script that will be called. For example, if your hspice script exists under /usr/meta/h9007/bin/hspice, then execute the following command to create the required symbolic link:

ln -s /usr/meta/h9007/bin/hspice /usr/bin/hspice

You must be in the root directory when executing the above command.

# **Running ELDO on a Remote Machine**

To run ELDO on the remote machine called *eldomach*, enter the following command:

eldorem eldo<anacad root>/eldo/<version>/com/eldo"eldomach" CANNOT PIPE

where,

<anacad\_root> and <version> are replaced with the home directory of the ANACAD

software and the current version number of ELDO, respectively.

eldorem represents the name of the simulator.

pipe creates an interprocess channel that responds to read/write calls.

### **Running Saber on a Remote Machine**

To run Saber on the remote machine called *sabermach*, enter the following command: saberrem saber /usr/saber/bin/saber "sabermach" CAN PIPE

where,

saberrem represents the name of the simulator and pipe creates an interprocess channel

that responds to read/write calls.

# **Running HPEESOFSIM on a Remote Machine**

To run HPEESOFSIM on the remote machine called *hpsimmach*, enter the following command:

hpsimrem hpeesofsim <simulator path> "hpsimmach" CAN\_PIPE

### where,

*hpsimrem* represents the name of the simulator and *pipe* creates an interprocess channel that responds to read/write calls.

hpeesofsim is the simulator name.

The third field is the path to the simulators location installed on the remote machine.

To launch an external simulation, copy the file \$ICCAP\_ROOT/bin/hpeesofsim\_start to some location on the remote machine. Modify the file (as explained within the file) to set HPEESOF\_DIR and HPEESOFSIMFRONT\_DIR for the remote machine. Then, ensure that hpeesofsim\_front is on the remote machine. If the remote machine contains the same OS as the local machine, then you can copy \$ICCAP\_ROOT/bin/hpeesofsim\_front from the local machine. If the remote machine has a different architecture, hpeesofsim\_front for all architectures can be found on your distribution CD under the subdirectory simlinks. Finally, modify the file usersimulators to refer to the remote host and the path to hpeesofsim\_start on the remote host.

# **Simulators in IC-CAP**

- ADS Simulator (simulation)

- SPECTRE Simulator (simulation)

- HSPICE Simulator (simulation)

- SPICE Simulators (simulation)

- ELDO Simulator (simulation)

- Saber Simulator (simulation)

# **ADS Simulator**

- About ADS Simulator (simulation)

- ADS Interfaces (simulation)

- System Requirements (simulation)

- Setting Environment Variables (simulation)

- ADS Simulation Example (simulation)

- Piped and Non-Piped ADS Simulations (simulation)

- Circuit Model Descriptions (simulation)

- ADS Parameter Sweeps (simulation)

- ADS Simulator Syntax (simulation)

### About ADS Simulator in IC-CAP

This section describes the details of using the Advanced Design System (ADS) Simulator with IC-CAP. For general information on IC-CAP simulation, refer to Simulation (simulation).

### 1 Note

The PC version of IC-CAP supports ADS version 2002 or newer. Older versions of ADS can not be used with the PC version of IC-CAP.

### IC-CAP supports the following ADS features:

- DC, Small Signal AC, Small Signal S-Parameter, and Transient analysis options

- Parameter sweeps for device and circuit simulation

- Temperature sweeps

- Hierarchical simulation

- Variables

- Constants

- Expressions

- Spectre circuit page

- Spice circuit page

The ADS Optimizer features are not currently supported in IC-CAP. IC-CAP optimization (different from the ADS Optimizer) of simulated data to target data is supported.

The ADS simulator supports the following analysis types:

- DC

- AC

- 2-port

- Multiport

- Transient

- Noise

- Capacitance Voltage (CV)

- Time-Domain Reflectometry (TDR)

- Steady State Harmonic Balance

#### **1** Note

2-port simulation with high frequency noise is supported to extract noise parameters such as noise figure, optimum source reflection coefficients, equivalent noise resistance data, minimum noise figure data, and equivalent noise temperature data.

IC-CAP does not add extra circuitry in order to perform a 2-port simulation since this is a standard type in ADS.

### **ADS Interfaces**

IC-CAP provides three template names to interface to the ADS simulator's Circuit and Test Circuit pages:

- hpeesofsim uses native ADS simulator syntax

- spmodeads uses spectre simulator syntax, and

- hspicemodeads uses hspice simulator syntax