**USER MANUAL**

# PathWave Test Sync Executive

**User Manual**

PATHWAVE

This User Manual describes the PathWave Test Sync Executive programming environment, which is based on Keysight's Hard Virtual Instrument (HVI) technology. HVI enables you to develop and execute synchronous, real-time operations across multiple instruments. The real-time sequencing and synchronization capabilities of PathWave Test Sync Executive make it a powerful tool for Multi-Input Multi-Output (MIMO) applications that require tight synchronization and real-time control and feedback.

### **Notices**

# Copyright Notice

© Keysight Technologies 2020

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

### Manual Part Number

PathWave Test Sync Executive User Manual

# Published By

Keysight Technologies PrintedInAddress\_Line1 PrintedInAddress\_Line2 PrintedInAddress\_Line3

#### Edition

Edition 1.021, October, 2020 PrintedInCountry

### Regulatory Compliance

This product has been designed and tested in accordance with accepted industry standards, and has been supplied in a safe condition. To review the Declaration of Conformity, go to http://www.keysight.com/go/conformity.

### Warranty

THE MATERIAL CONTAINED IN THIS

DOCUMENT IS PROVIDED "AS IS," AND

IS SUBJECT TO BEING CHANGED,

WITHOUT NOTICE, IN FUTURE

EDITIONS. FURTHER, TO THE

MAXIMUM EXTENT PERMITTED BY

APPLICABLE LAW, KEYSIGHT

DISCLAIMS ALL WARRANTIES, EITHER

EXPRESS OR IMPLIED. WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR OF ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT SHALL CONTROL.

KEYSIGHT TECHNOLOGIES DOES NOT WARRANT THIRD-PARTY SYSTEM-LEVEL (COMBINATION OF CHASSIS, CONTROLLERS, MODULES, ETC.) PERFORMANCE, SAFETY, OR REGULATORY COMPLIANCE, UNLESS SPECIFICALLY STATED.

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license

# U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial

computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at

http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than

Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

# Safety Notices

#### **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

The following safety precautions should be observed before using this product and any associated instrumentation.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation, operation, and maintenance information carefully before using the product.

#### WARNING

If this product is not used as specified, the protection provided by the equipment could be impaired. This product must be used in a normal condition (in which all means for protection are intact) only.

The types of product users are:

- Responsible body is the individual or group responsible for the use and maintenance of equipment, for ensuring that the equipment is operated within its specifications and operating limits, and for ensuring operators are adequately trained.

- Operators use the product for its intended function. They must be trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with hazardous live circuits.

Maintenance personnel perform routine procedures on the product to keep it operating properly (for example, setting the line voltage or replacing consumable materials). Maintenance procedures are described in the user documentation. The procedures explicitly state if the operator may perform them. Otherwise, they should be performed only by service personnel.

Service personnel are trained to work on live circuits, perform safe installations, and repair products. Only properly trained service personnel may perform installation and service procedures.

### WARNING

Operator is responsible to maintain safe operating conditions. To ensure safe operating conditions, modules should not be operated beyond the full temperature range specified in the Environmental and physical specification. Exceeding safe operating conditions can result in shorter lifespans, improper module performance and user safety issues. When the modules are in use and operation within the specified full temperature range is not maintained, module surface temperatures may exceed safe handling conditions which can cause discomfort or burns if

touched. In the event of a module exceeding the full temperature range, always allow the module to cool before touching or removing modules from chassis.

Keysight products are designed for use with electrical signals that are rated Measurement Category I and Measurement Category II, as described in the International Electrotechnical Commission (IEC) Standard IEC 60664. Most measurement, control, and data I/O signals are Measurement Category I and must not be directly connected to mains voltage or to voltage sources with high transient over-voltages. Measurement Category II connections require protection for high transient over-voltages often associated with local AC mains connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise marked or described in the user documentation.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential human contact. Product

operators in these circumstances must be trained to protect themselves from the risk of electric shock. If the circuit is capable of operating at or above 1000V, no conductive part of the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance-limited sources. NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, ensure that the line cord is connected to a properly-grounded power receptacle. Inspect the connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input power disconnect device must be provided in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its specifications and operating instructions, or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with the same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a lid interlock.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits – including the power transformer, test leads, and input jacks – must be purchased from Keysight. Standard fuses with applicable national safety approvals may be used if the rating and type are the same. Other components

that are not safety-related may be purchased from other suppliers as long as they are equivalent to the original component (note that selected parts should be purchased only through Keysight to maintain accuracy and functionality of the product). If you are unsure about the applicability of a replacement component, call an Keysight office for information.

### WARNING

No operator serviceable parts inside.

Refer servicing to qualified personnel.

To prevent electrical shock do not remove covers. For continued protection against fire hazard, replace fuse with same type and rating.

### PRODUCT MARKINGS:

The CE mark is a registered trademark of the European Community.

Australian Communication and Media Authority mark to indicate regulatory compliance as a registered supplier.

dispose in domestic household waste. To return unwanted products, contact your local Keysight office, or for more information see

http://about.keysight.com/en/companyinfo/e nvironment/takeback.shtml.

during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of the product.

# ICES/NMB-001 ISM GRP.1 CLASS A

This symbol indicates product compliance with the Canadian Interference-Causing Equipment Standard (ICES-001). It also identifies the product is an Industrial Scientific and Medical Group 1 Class A product (CISPR 11, Clause 4).

South Korean Class A EMC Declaration. This equipment is Class A suitable for professional use and is for use in electromagnetic environments outside of the home. A 급 기기 (업무용 방송통신 기자재)이 기기는 업무용(A급)전자파적 합기기로서 판 매자 또는 사용자는 이 점을 주 의하시기 바라 며, 가정외의 지역에서 사 용하는 것을 목적으로 합니다.

This symbol on an instrument means caution, risk of danger. You should refer to the operating instructions located in the user documentation in all cases where the symbol is marked on the instrument.

This product complies with the WEEE Directive marketing requirement. The affixed product label (above) indicates that you must not discard this electrical/electronic product in domestic household waste. Product Category: With reference to the equipment types in the WEEE directive Annex 1, this product is classified as "Monitoring and Control instrumentation" product. Do not

This symbol indicates the instrument is sensitive to electrostatic discharge (ESD). ESD can damage the highly sensitive components in your instrument. ESD damage is most likely to occur as the module is being installed or when cables are connected or disconnected. Protect the circuits from ESD damage by wearing a grounding strap that provides a high resistance path to ground. Alternatively, ground yourself to discharge any builtup static charge by touching the outer shell of any grounded instrument chassis before touching the port connectors.

This symbol indicates the time period

# Contents

| (; | S2201A - PathWave Test Sync Executive User Manual   | 8   |

|----|-----------------------------------------------------|-----|

|    | Chapter 1: Introduction                             | 9   |

|    | Chapter 2: Installing PathWave Test Sync Executive  | 11  |

|    | System Requirements                                 | 12  |

|    | Install Main Components                             | 14  |

|    | Install Additional Components                       | 22  |

|    | Chapter 3: Installing Licenses                      | 24  |

|    | Chapter 4: HVI Elements                             | 32  |

|    | About Instruments                                   | 32  |

|    | About PathWave Test Sync Executive                  | 33  |

|    | HVI API Use Model                                   | 34  |

|    | HVI Engines                                         | 35  |

|    | HVI Resources                                       | 36  |

|    | HVI Sequences and Statements                        | 38  |

|    | HVI Sequences                                       | 39  |

|    | HVI Statements                                      | 41  |

|    | HVI Diagrams                                        | 50  |

|    | HVI Timing                                          |     |

|    | Chapter 5: The HVI API                              | 68  |

|    | HVI API Functionality                               |     |

|    | HVI API Organization                                |     |

|    | SystemDefinition                                    |     |

|    | Synchronization resources and clocks                |     |

|    | EngineDefinition                                    | 75  |

|    | Chassis and Interconnect                            |     |

|    | Sequencer                                           |     |

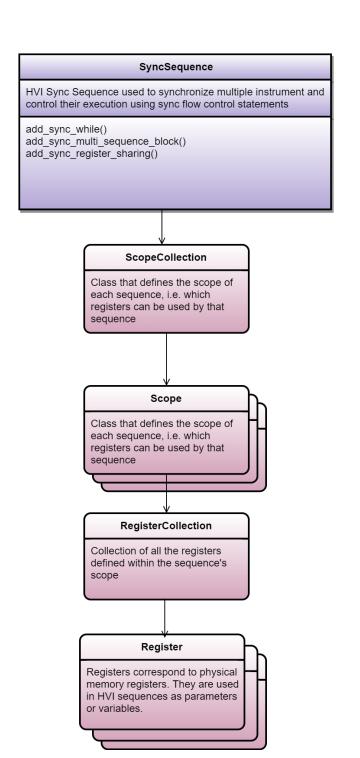

|    | HVI SyncSequence and Sequence                       | 87  |

|    | HVI API Statements                                  |     |

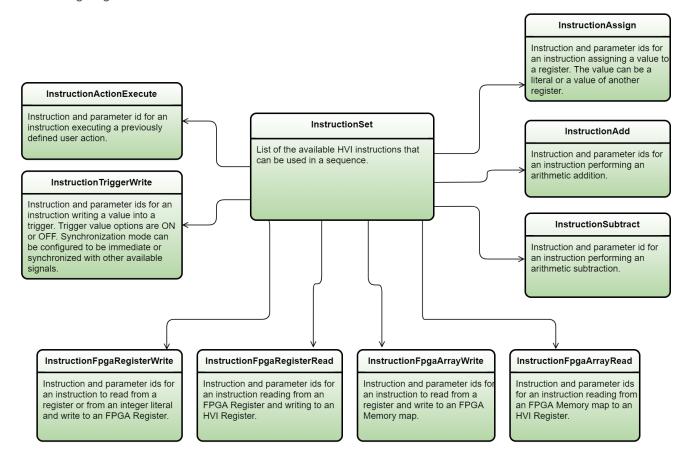

|    | InstructionSet                                      |     |

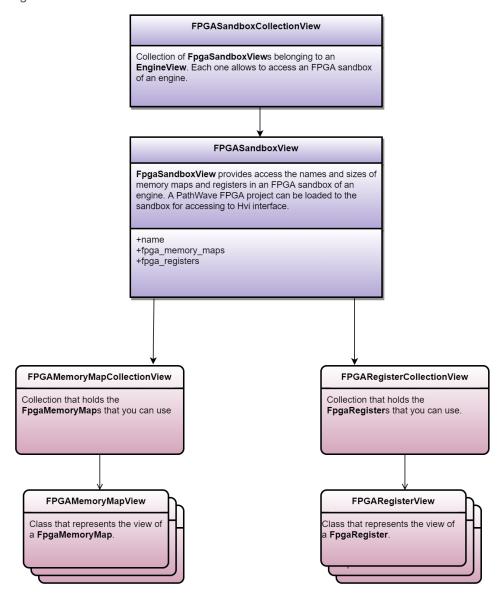

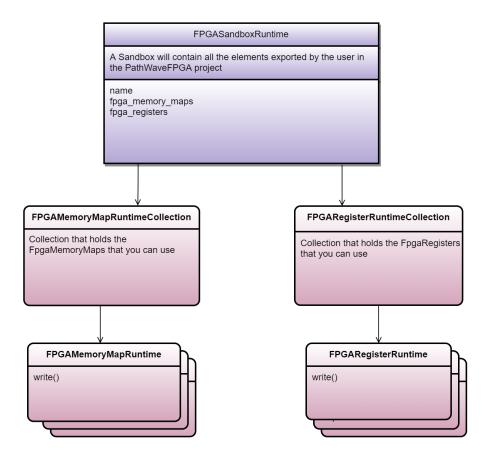

|    | FPGA Sandbox View                                   |     |

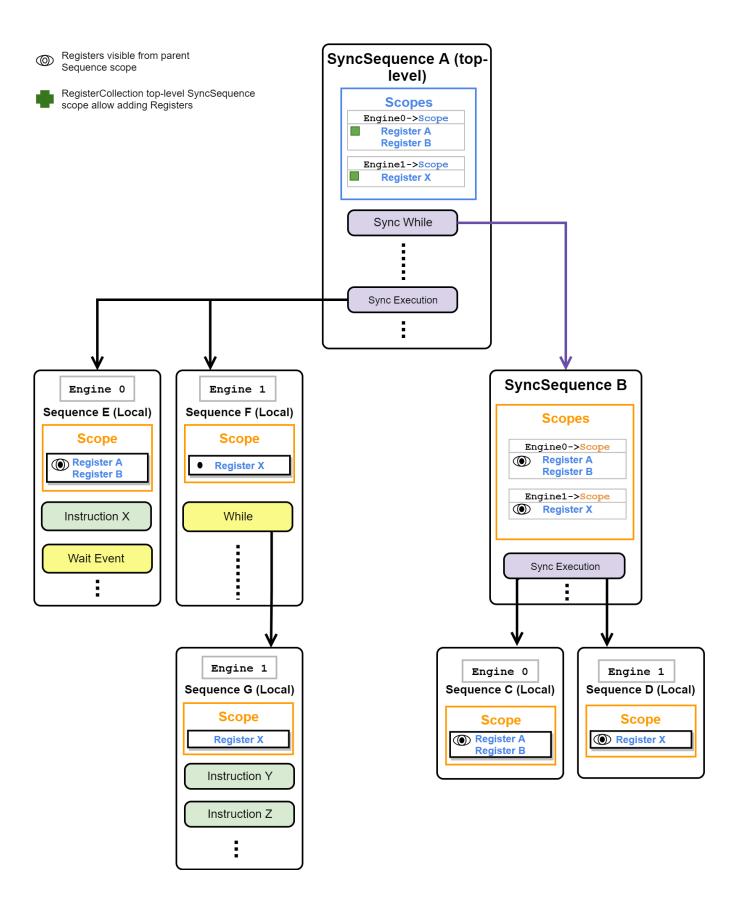

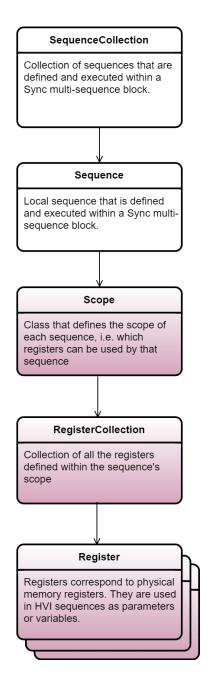

|    | HVI Registers and Scopes                            |     |

|    | HVI Compilation                                     |     |

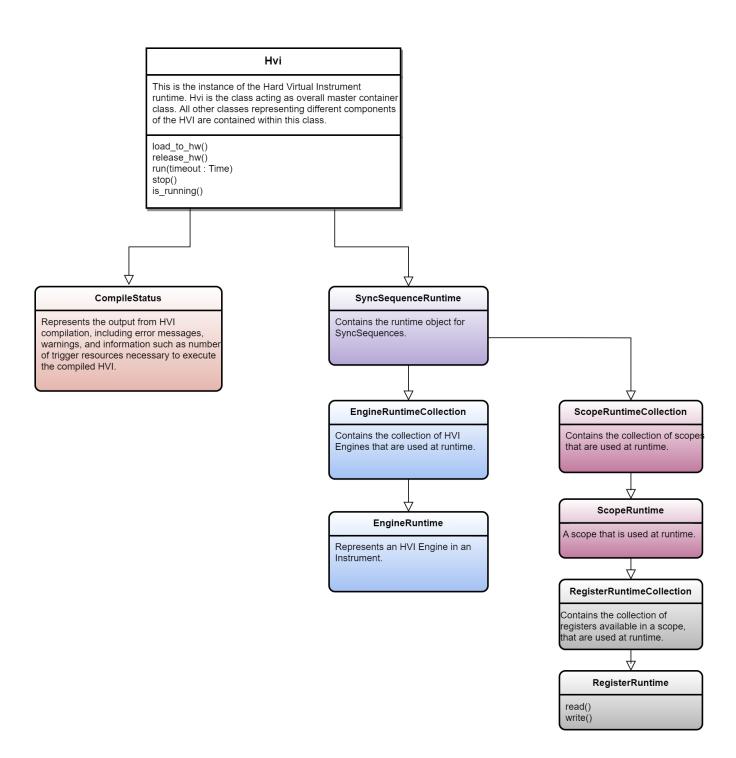

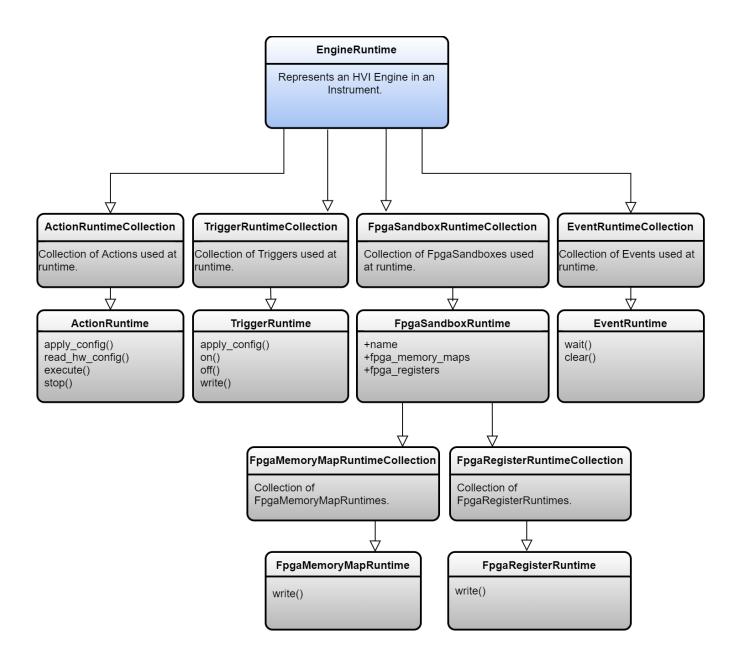

|    | Hvi                                                 |     |

|    | Load to Hardware and Run                            |     |

|    | Chapter 6: Building an Application with the HVI API | 119 |

| Chapter 7: HVI Time Management and Latency        | .131 |

|---------------------------------------------------|------|

| Appendix A: Supported instruments                 | .153 |

| Appendix B: Additional Documentation and Examples | 155  |

# KS2201A - PathWave Test Sync Executive User Manual

This User Manual describes the PathWave Test Sync Executive programming environment, which is based on Keysight's Hard Virtual Instrument (HVI) technology. HVI enables you to develop and execute synchronous, real-time operations across multiple instruments. The real-time sequencing and synchronization capabilities of PathWave Test Sync Executive make it a powerful tool for Multi-Input Multi-Output (MIMO) applications that require tight synchronization and real-time control and feedback.

NOTE PathWave Test Sync Executive (KS2201A) is **not compatible** with the previous version, M3601A. You cannot use them together and they cannot run the same Sequences.

# **Chapter 1: Introduction**

This chapter introduces Keysight KS2201A, PathWave Test Sync Executive and HVI technology.

### About Keysight PathWave Test Sync Executive

PathWave Test Sync Executive is a programming environment based on Keysight's *Hard Virtual Instrument* (HVI) technology, that enables you to develop and execute synchronous real-time operations across multiple instruments.

The real-time sequencing and synchronization capabilities of PathWave Test Sync Executive make it a powerful tool for *Multi-Input Multi-Output* (MIMO) applications that require tight synchronization and real-time control and feedback. For example:

- Radar.

- Bit error testing.

- · Communication systems.

- Massive-scale quantum physics experiments.

PathWave Test Sync Executive supports:

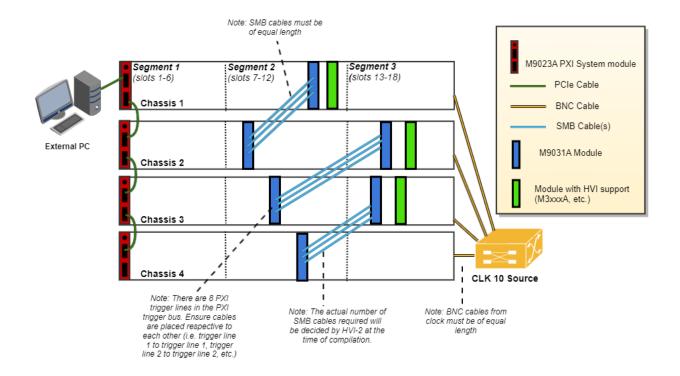

- Multi-chassis configuration.

- HVI sequence design using an Application Programming Interface (API) for Python.

- Programming of multiple instruments.

- Execution of time-deterministic sequences of operations.

- Precision synchronization and execution.

# About HVI Technology

HVI technology enables you to program one or more instruments to execute time-deterministic sequences of operations with precise synchronization. It achieves this by deploying a code executable onto the hardware of each instrument. This executes on an *HVI Engine*, an IP block. or processor, integrated into the instrument. The code executes on these Engines in parallel, across multiple instruments. The new user-defined hardware operation of the group of instruments is called a Hard Virtual Instrument or just HVI. The sequences of operations or instructions executed by the HVI engines are called HVI Sequences. The operations and instructions that make up sequences are known as HVI Statements.

When creating an HVI, you can include any instrument with HVI support. The Keysight M3xxxA family of PXI instruments is one product family with HVI support. This user manual includes code examples from the SD1/M3xxxA API. These snippets complement the code examples that explain functionality of the HVI API.

### **HVI Application Programming Interface**

The HVI API is the set of programming classes and methods that enable you to create and program an HVI instance. The HVI API 2020 release 1 supports the Python language. Support for more programming languages including C#/.NET are planned for future releases. This document refers to the Python API in explanations. A complete description of the HVI Python API is provided in the help file with the PathWave Test Sync Executive installer, available at:

C:\Program Files\Keysight\Pathwave Test Sync Executive 2020\api\python\Help

### API Use Model: HVI API versus HVI instrument specific API

Each instrument extends the HVI API functionality with an instrument specific API. The HVI API is common to all products and only the instrument specific HVI API is different, depending on the instrument. It is important to differentiate between the HVI-native API features and the instrument-specific extensions, which enable an heterogeneous array of instruments and resources to coexist in a common framework.

The HVI-native API exposes all HVI functions and is a common API for all products. It defines the base interfaces and classes that are used to create an HVI, control the hardware execution flow, and operate with data, triggers, events and actions, but it alone does not include the ability to control instrument-specific operations. The HVI API defines the hard virtual instrumentation framework, and it is the job of the instrument-specific HVI API extensions to enable instrument functions in an HVI. These functions are exposed by the instrument-specific add-on definitions, this is done by an HVI instrument add-on API provided by each instrument that describes the instrument-specific resources and operations that can be executed or used within HVI sequences:

For HVI instrument-specific definitions of the Keysight M3xxxA PXI product family, see:

SD1 3.x Software for M320xA / M330xA Arbitrary Waveform Generators User's Guide.

and

SD1 3.x Software for M310xA / M330xA Digitizers User's Guide.

# Chapter 2: Installing PathWave Test Sync Executive

This chapter explains how to install PathWave Test Sync Executive and related required components.

It contains the following sections:

- System Requirements

- Install Main Components

- Install Additional Components

NOTE

PathWave Test Sync Executive (KS2201A) and the previous version M3601A, are not compatible. You cannot use them together.

Also, if you use M3601A, the additional components required use different versions, so they must be reinstalled every time you change between between running M3601 and KS2201A.

# System Requirements

This section describes the system requirements for PathWave Test Sync Executive.

### PathWave Test Sync Executive installation requirements

To install PathWave Test Sync Executive you require the following:

- Python 3.7.x, 64-bit.

- Keysight PathWave Test Sync Executive installer.

To install these, see Install Main Components.

### Additional components required

To run PathWave Test Sync Executive with hardware, you require

- One or more PXIe chassis.

- One or more PXIe instruments.

- · Associated software, libraries, drivers and firmware.

### Chassis

PathWave Test Sync Executive is compatible with any PXIe chassis, however Keysight recommends you use the following Keysight chassis so you can make use of their capabilities and multi-instrument and multi-chassis scalability:

- M9019A.

- M9018B.

- M9010A.

These chassis include an enhanced PXI trigger bridge that provides the capabilities required by PathWave Test Sync Executive to provide support for multi-segment/chassis operation. You can use other chassis without limitation for single segment operation, and you can also use other chassis for multi-segment/multi-chassis operations, but there are limitations in terms of the complexity of the HVI sequences that you can execute.

For most chassis, the enhanced PXI trigger bridge functionality is delivered by a firmware update, see your chassis user manual for details. The Pathwave Test Sync Executive programming examples (www.keysight.com/find/KS2201A-programming-examples) show how to verify the correct firmware version for specific chassis.

### Instruments

For information about compatibility, software and firmware versions requirements for specific PathWave Test Sync Executive releases, and firmware update procedures, see your instrument documentation.

For more information see the and PathWave Test Sync Executive *Release Notes* and Appendix A: Supported instruments.

# Install Main Components

This section explains how to install the main components of PathWave Test Sync Executive, it contains the following sections:

- 1. Install Python 3.7.x, 64-bit.

- 2. Install PathWave Test Sync Executive.

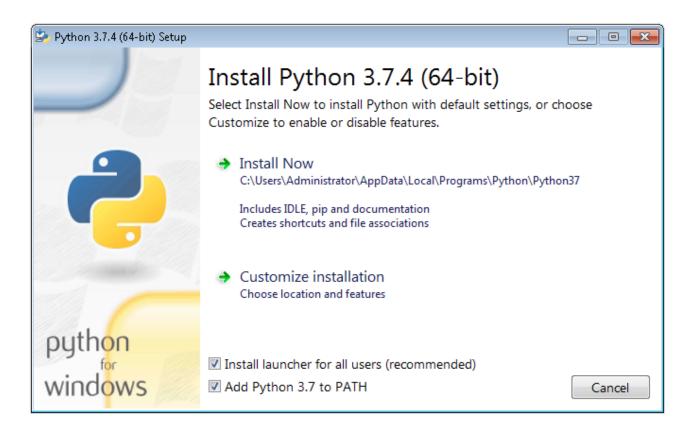

### 1: Install Python 3.7.x, 64-bit

PathWave test Sync Executive requires Python 64-bit version 3.7.x

- 1. Download the Python installer from the Python web site: python.org.

- 2. Run the installer.

- a. Add Python 3.7.x to the PATH system Variable. To do this, ensure the check-box **Add python 3.7 to PATH** is checked. This is shown in the following screenshot:

# 2: Install PathWave Test Sync Executive

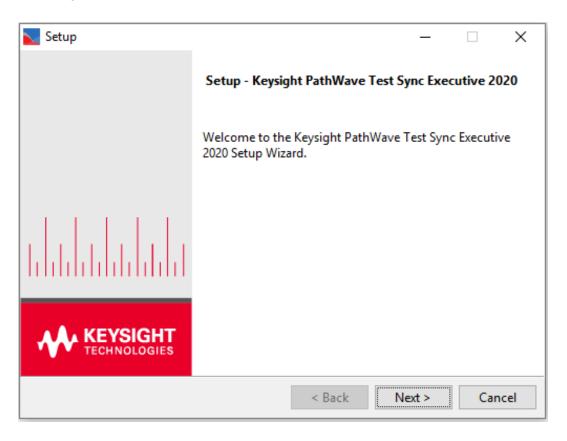

Use the following procedure to install PathWave Test Sync Executive:

NOTE You must install Python 3.7.x 64-bit before installing PathWave Test Sync Executive.

Execute the installer file:

The **Setup** screen is shown:

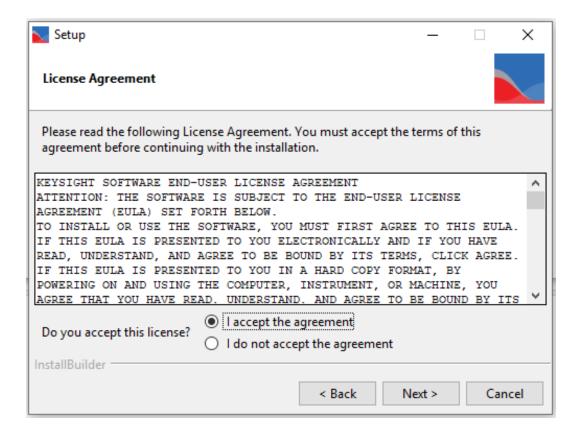

The next screen is the License Agreement screen. You must accept the license to continue:

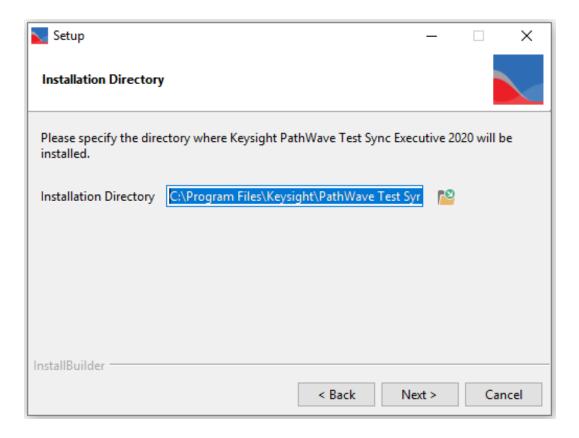

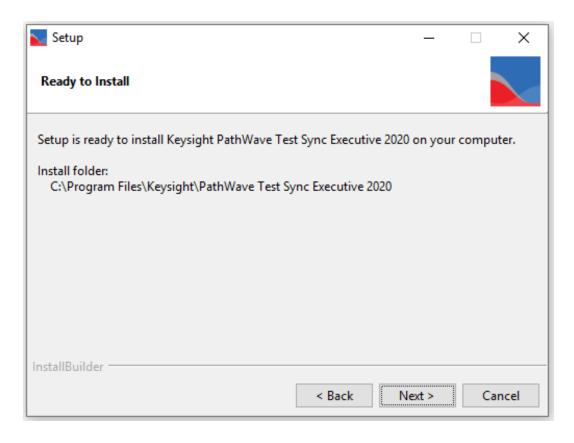

You can change the installation directory on the **Installation Directory** screen.

By default, PathWave Test Sync Executive is installed to:

C:\Program Files\Keysight\PathWave Test Sync Executive 2020

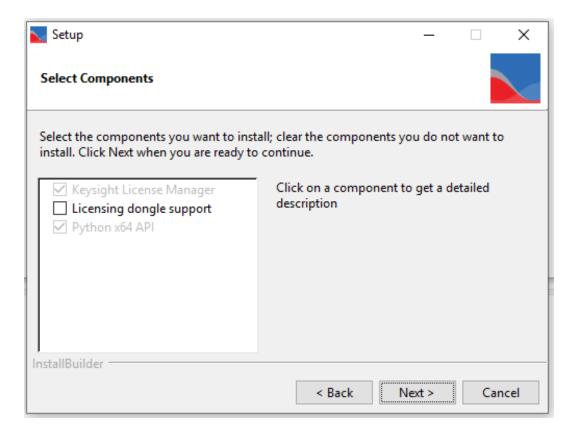

The **Select Components** screen enables you to select the components you want to install.

Required components are selected by default and you cannot de-select them.

When you have selected the components, the next screen is **Ready to Install**. Select **Next** to install PathWave Test Sync Executive.

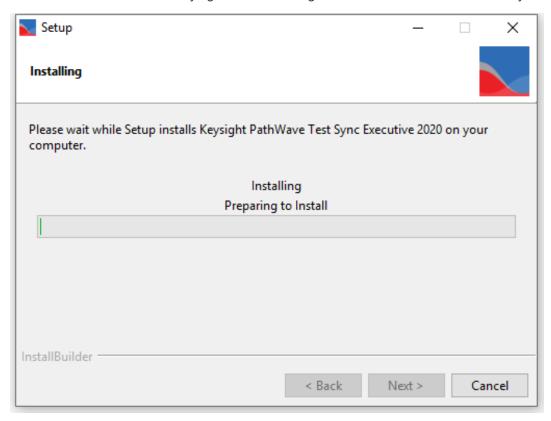

The Installer first installs the Keysight License manager. It then installs PathWave Test Sync Executive:

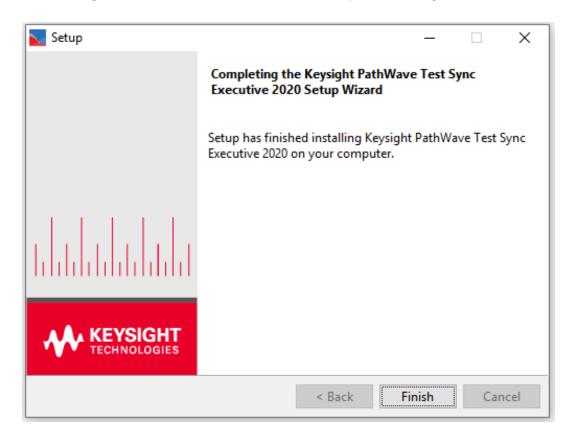

The following screen is shown when the installer has completed installing: Select **Finish** to close the installer.

# Install Additional Components

To use PathWave Test Sync Executive, you require both hardware and software. Ensure you have all of the following components and they are up to date:

- 1. Keysight IO Libraries.

- 2. Keysight SD1 Drivers, Libraries, and Software Front Panel.

- 3. Keysight Instrument FPGA Firmware.

- 4. Keysight Chassis Driver and Firmware.

# Install Keysight IO Libraries

Install the IO Libraries, these are available on www.keysight.com.

# Install Keysight SD1 Drivers, Libraries, and SD1 Software Front Panel

Install the SD1 Libraries and driver, both of these are available on <a href="www.keysight.com">www.keysight.com</a>. When you install the Keysight SD1 Driver, SD1 Software Front Panel (SFP) software is automatically installed.

NOTE Ensure you check the SD1 driver release notes, so that you install a SD1 driver that is compatible with the version of PathWave Test Sync Executive you have installed.

### Update Keysight Instrument FPGA Firmware

You can update the FPGA firmware of your PXI instruments from the Hardware Manager window of the SD1 SFP. For information about how to install SW and FPGA firmware for SD1 and M3xxxA Keysight instruments, see the documents:

- Keysight M3xxxA Product Family Firmware Update Instructions.

- M3xxxA User Guide.

These are available on www.keysight.com.

NOTE Ensure you check the M3xxxA firmware release notes, so that you install a driver that is compatible with the version of PathWave Test Sync Executive you have installed.

# Install Keysight Chassis Family Driver

Install the Chassis Family Driver, this is available on <a href="www.keysight.com">www.keysight.com</a>. When you install the Keysight Chassis Family Driver, PXIe Chassis Software Front Panel (SFP) software is automatically installed.

### Update Keysight Chassis Firmware

In PXIe Chassis Software Front Panel you can:

- · Check the chassis firmware version in the help window.

- Update the chassis firmware with the Utilities window of PXIe Chassis SFP.

You can use the Utilities window of PXIe Chassis SFP to update the chassis firmware. For more information about updating Chassis firmware, see *PXIeChassisFirmwareUpdateGuide.pdf*on www.keysight.com.

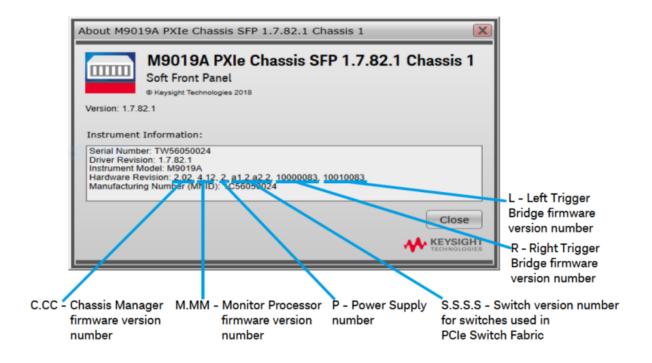

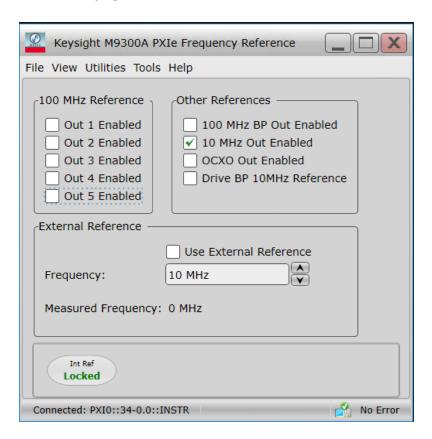

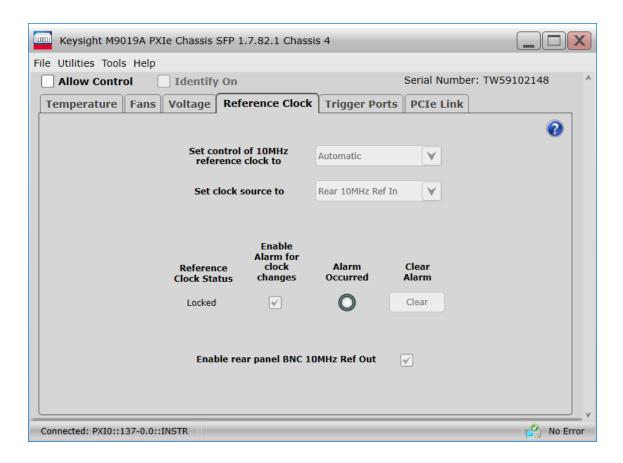

The following screenshot shows an example of the chassis firmware version shown in the help window of the PXIe Chassis SFP. In this case the chassis is a Keysight Chassis model M9019A.

M9019A Firmware Version Components

| Firmware Component                                            | 2017      | 2018      | 2019StdTrig | 2019EnhTrig |

|---------------------------------------------------------------|-----------|-----------|-------------|-------------|

| Chassis Manager                                               | 2.02      | 2.02      | 2.02        | 2.02        |

| Monitor Processor                                             | 3.11      | 3.11      | 4.12        | 4.12        |

| Switch version number for switches used in PCIe Switch Fabric | a1.2.a2.2 | a1.2.a2.2 | a1.2.a2.2   | a1.2.a2.2   |

| Right Trigger Bridge                                          | 0         | 10000083  | 0           | 10000083    |

| Left Trigger Bridge                                           | 0         | 10010083  | 0           | 10010083    |

# Chapter 3: Installing Licenses

This chapter explains how to install PathWave Test Sync Executive licenses. It contains the following sections:

- About PathWave Test Sync Executive Licenses.

- Installing Licenses with Keysight License Manager.

# About PathWave Test Sync Executive Licenses

PathWave Test Sync Executive requires one license per chassis that is used in your HVI implementation. If you are using one chassis and want to use a second chassis, you are required to purchase and install at least two licenses to use the second chassis. All HVI instances running in the same process share the same licenses, but HVI instances running on different processes require different licenses. For example:

| Description                                                   | Licenses required |

|---------------------------------------------------------------|-------------------|

| 1 HVI instance using 1 chassis                                | 1                 |

| 2 HVI instances in the SAME process using 1 chassis each      | 1                 |

| 3 HVI instances in the SAME process using 2 chassis each      | 2                 |

| 2 HVI instances in 2 DIFFERENT processes using 1 chassis each | 2                 |

| 3 HVI instances in 3 DIFFERENT processes using 2 chassis each | 6                 |

### Supported licensing modes

The following types of licenses are supported:

### Commercial licenses:

- Node-Locked, perpetual and 6, 12, 24, and 36 months, time based.

- USB Portable, perpetual and 6, 12, 24, and 36 months, time based.

- Floating/Networking, perpetual and 6, 12, 24, and 36 months, time based.

#### Trial licenses:

• 90 days Node-locked.

### Installing Licenses with Keysight License Manager

You can install licenses from the Keysight License Manager. This is installed when you install **Keysight Test Sync Executive**. You can use a local license on your computer, or a floating license from a license server.

The licensing process

The Keysight licensing process uses the following steps:

### 1. Purchase and fulfillment

For most Keysight licensed product options, your entitlement certificate is sent to you as a PDF attachment via email immediately after your purchase. In some cases, you receive a paper copy of your certificate with your purchased product. The licensed product options may be software products or upgraded features of an instrument.

### 2. Getting a license

Using the entitlement certificate you received when you ordered, you can request your licenses on the Keysight Software Manager web site. To do this, you'll need to choose a host instrument or PC, and provide its identifying information (the Host ID) when you request your licenses. Once you begin the process, Keysight Software Manager will guide you step by step through requesting your licenses and you will receive the license files via email.

You may need to create a *myKeysight* login when you first go to the Keysight Software Manager site, and you will need to log in anytime you go to the site.

### 3. Installing your license

After you receive a license file from Keysight Software Manager, you must install it on your instrument or computer or on a central licensing server accessible from your instrument or computer, to enable the licensed software.

To install the license:

- 1. Install PathWave Test Sync Executive.

- 2. Update the vendor daemon that is included in Keysight License Manager 6:

- a. Download Keysight License Server version 2019.05.17 from https://www.keysight.com/find/licenseserver. This is a .zip file.

- b. Extract the file agilesofd.exe from the zip file and save it in c:\Program Files\Common Files\Keysight\License Manager 6\bin Overwriting the version that was installed there. You will be asked for administrator permissions to do this.

- 3. Use Keysight License Manager to install your license.

For fully comprehensive information on Keysight licensing, including setup and troubleshooting information, see the *Keysight Licensing Administrator's Guide*. This is installed with this licensing software at:

C:\Program Files\Common Files\Keysight\License Manager 6.

It is also available at http://www.keysight.com/find/licensingdoc.

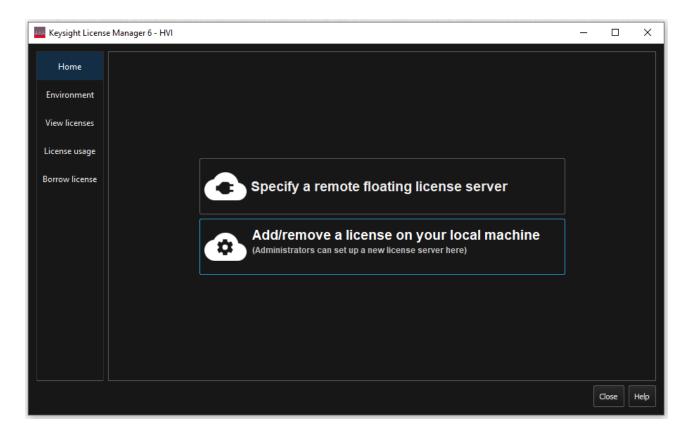

Keysight License Manager

Keysight License Manager 6 (KLM 6) is installed with PathWave Test Sync Executive.

All the options are explained in the Help file which you can get by selecting **Help**.

C:\Program Files\Common Files\Keysight\License Manager 6\bin\help\Content

The following image shows the Keysight License Manager home screen:

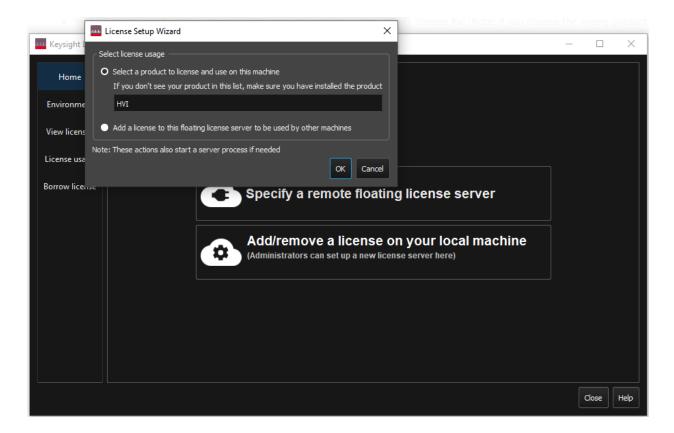

### Adding a local license

If you have a node-locked license, you must add the license to the machine that shall be using the license.

If you have a floating license, you must add the license to the license server machine; this can be the machine that shall use the license, or it can be a different machine.

To add a license on a machine:

- 1. Copy the license to a temporary location on the machine.

- 2. In Keysight License Manager 6, select **Add/remove a license on your local machine**. A window called **License Setup Wizard** appears.

- 3. Select: Select a product to license and use on this machine.

- 4. Select HVI from the list and press OK.

The following image shows the Keysight License Manager home screen with the **License Setup Wizard** window.

| After you click OK, a dialog appears to let you add the license from the temporary location in step 1. The license is copied to a folder managed by KLM 6. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

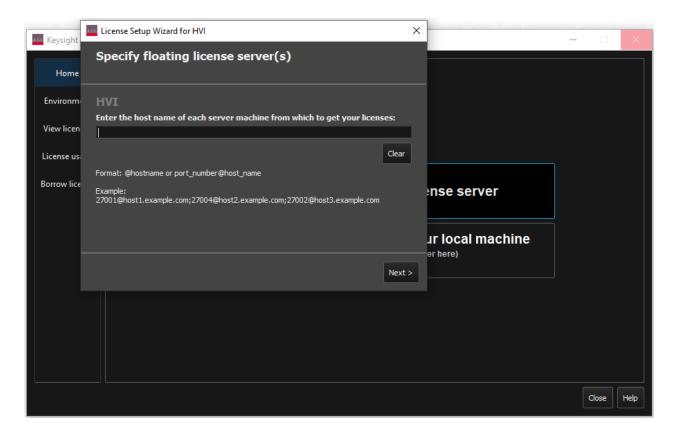

### Adding a license server

If you set up a floating license on a license server machine, follow this procedure to use the license on a different machine.

To add a license server:

- Select Specify a remote floating license server.

A window called License Setup Wizard for HVI appears.

- 2. Enter the server or servers in the field: **Enter the host Name of each server machine from which to get your license**.

These must be in the format @hostName or port number@hostName.

3. To complete the setup, select **Next >**.

The following image shows the Keysight License Manager home screen with the **License Setup Wizard for HVI** window:

### Borrowing a floating license

Some floating licenses can be borrowed. Borrowing lets you check out a license for an extended period of time and use it offline, without a connection to the network license server.

The borrow works in the following steps:

- 1. You must be connected to the network, with access to a license server that has floating licenses for the product you need to use.

- 2. Choose the license or licenses you want to borrow and specify a return date. You can typically borrow a license for up to 365 days, or until it expires, whichever comes first.

- 3. When you have borrowed the license(s) you require, you can disconnect your local machine from the network, and use the licensed product offline. No one else can use that specific license count during the borrow period: The server will report it as being in use and will deny checkout requests for that license count.

- 4. The borrow ends in one of two ways:

- At any time, you can reconnect your machine to the network and return the license.

- If you do not return the license before the return date, the license will automatically be returned, even if

your machine is not connected to the network. Once the license is returned, you can no longer use the

licensed product/feature, and the license server considers the license count available to be checked out

or borrowed by another client.

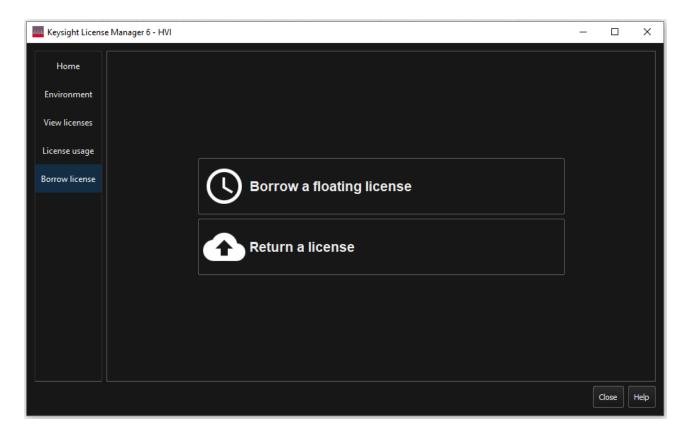

The following image shows the Keysight License Manager **Borrow License** page.

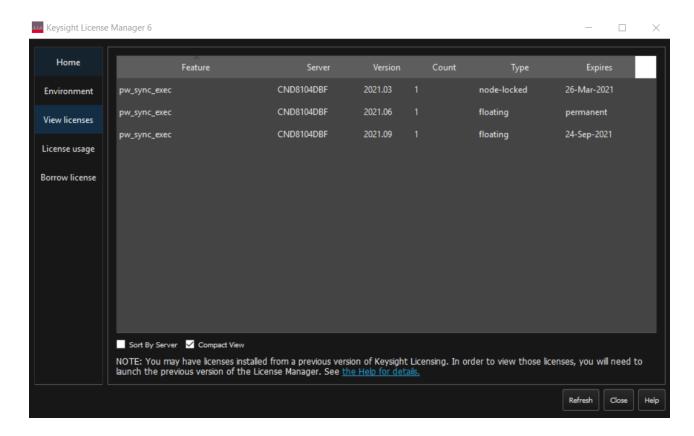

### View licenses

To view your licenses, select **View Licenses**. This is shown in the following image:

# Troubleshooting

By default, KLM 6 saves its log files in C:\ProgramData\Keysight\Licensing\Log.

# Chapter 4: HVI Elements

This chapter describes the elements that make up an HVI.

It contains the following sections:

- About Instruments

- About PathWave Test Sync Executive

- HVI API Use Model

- HVI Engines

- HVI Resources

- HVI Sequences and Statements

- HVI Sequences

- HVI Statements

- HVI Diagrams

- HVI Timing

### **About Instruments**

Instruments are modules or cards that can capture or generate various kinds of electronic signals. Many kinds of instruments are available with different kinds of functions.

Different kinds of instruments can perform various functions with electronic signals:

- · Measure signals.

- · Record signals.

- · Perform signal analysis.

- · Perform signal conditioning.

Some types of instruments can generate different kinds of outputs:

- Signals.

- · Voltages.

- Pulses.

- · Arbitrary waveforms.

- Digital outputs.

Instruments can be supplied as modules or cards that fit into a chassis. The chassis enables you to fit multiple modules together. The instruments in a chassis are synchronized to a common digital clock reference that is shared by all of the instruments. The chassis also offers shared triggering and communication resources.

For this User Manual, the specific instruments referred to are PXI modular instruments that are inserted into a PXI chassis.

For a full list of Keysight instruments, see Keysight.com.

# About PathWave Test Sync Executive

PathWave Test Sync Executive enables you to program multiple instruments together so they can operate tightly orchestrated together with other instruments, like one instrument.

PathWave Test Sync Executive enhances individual instruments by enabling them to:

- Execute real-time sequences of operations with full time determinism.

- · Precisely synchronize instruments operations.

- Fast exchange information and decisions among instruments in real-time by hardware.

You define a new virtual instrument made up of a combination of instruments. This is known as a *Hard Virtual instrument* (HVI). Once the HVI resources are defined, you can program multiple instruments to work together as they were a single instrument.

To program the HVI you write an application. When you run your application, it generates the HVI instance and the binary code that executes by hardware on the instruments.

When creating an HVI, you can include any instrument that supports PathWave Test Sync Executive. For example, Keysight's M3xxxA family of PXI instruments.

Each instrument that supports PathWave Test Sync Executive has specific instructions that enable you to use its functionalities within HVI. These instructions are documented in the instrument documentation.

### HVI API Use Model

This section describes the HVI API use model, and the steps it involves.

HVI uses a program-within-a-program model, that is, HVI can be seen as a real-time hardware program that runs within a software program.

To use the HVI API, your application must follow a series of steps to define and run an HVI instance. These steps are broadly defined by three different classes within the HVI API:

- 1. SystemDefinition

- 2. HVI sequencer

- 3. Hvi

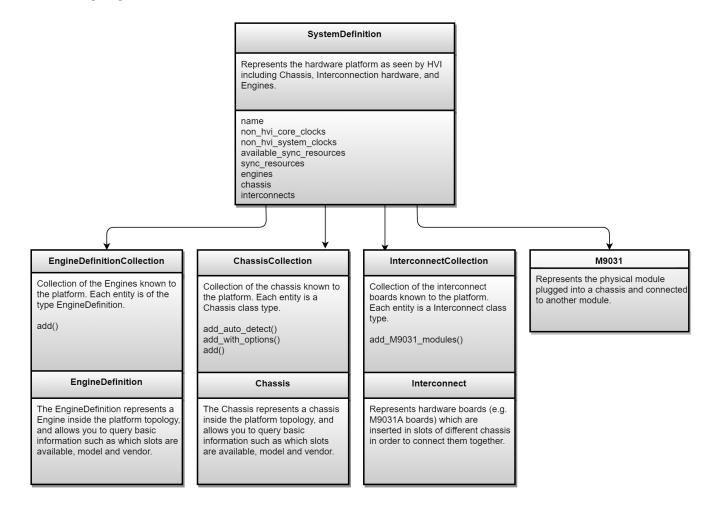

# SystemDefinition

You use this class to define all the instrument and platform resources that are required to set up the HVI:

You use this class to define:

- · Chassis.

- Interconnects.

- Clocks.

- Synchronous signals.

- · Trigger routing.

You also use this class to define the resources that are available on the instruments:

- Engines

- · Triggers.

- Actions.

- Events.

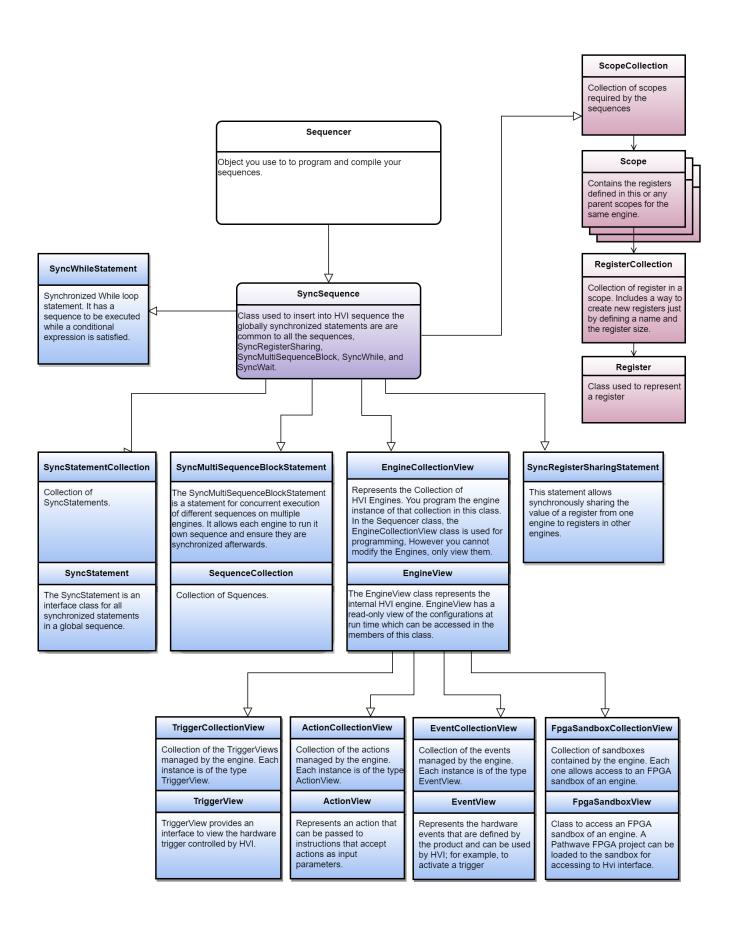

When you have defined these resources, you must register them within the relevant collections. Collections are special classes that associate resources with individual Engines so that you can use the resources on those Engines.

# HVI sequencer

You use this class to program and compile your sequences.

You add instructions and operations known as *statements* to *sequences*. These can be synchronized across instruments or local to a specific instrument.

You also add and use HVI Registers within this class. Registers are small, fast memories on the Engines that you can use as program Variables.

Once you have defined all the Sequences that define your HVI, you must compile it. If successful, the compilation process returns the HVI instance Hvi.

#### Hvi

Hvi is the runtime or executable object in HVI technology. With this object, you load the Sequences into the relevant Engines and execute them.

This class also enables you to interact with the hardware resources assigned to the HVI and initialize all resources before the actual execution happens.

### **Execution flow**

When you run your application, the HVI instance is generated, compiled, and downloaded into the instruments and infrastructure. It is executed across all the instruments and the infrastructure resources, and then the HVI instance takes control of the individual instruments and platform components. The HVI configures the required resources and downloads the hardware programs that, when executed, run on the instruments and platform hardware synchronously.

An application can create multiple HVI instances, but if the resources are shared, only one can be downloaded and executed in hardware at a time. If the HVI instances do not share any resources, they can be executed in parallel.

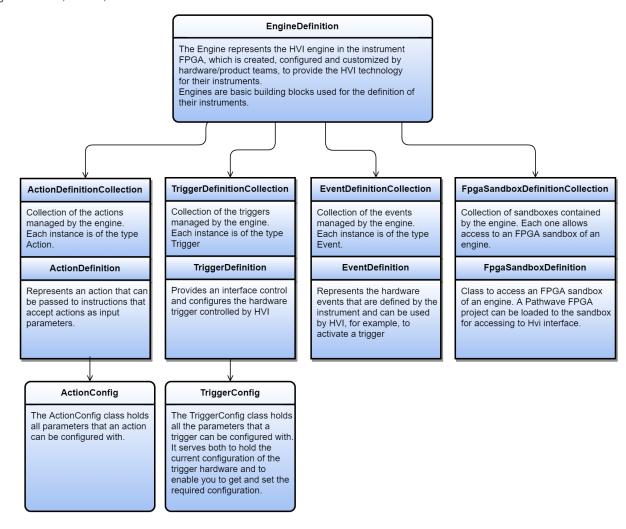

# **HVI** Engines

For HVI to control an instrument, the instrument requires one or more *HVI Engines*. An HVI Engine is an *Intellectual Property* (IP) block that controls the functions of the instrument and the timing of operations. The HVI Engine is included directly in the instrument hardware or it can be programmed into a *Field programmable Gate Array* (FPGA) in the instrument.

HVI works by deploying a binary executable to each hardware instrument to be executed by the HVI Engine. Different binaries execute on the different HVI Engines in parallel, across multiple instruments.

When you write an application that includes an HVI, you create HVI sequences. These are sequences of HVI Statements, these are operations that controls the instrument. The HVI Sequences are compiled into the binary executables that the HVI Engine executes.

### **HVI** Resources

The HVI Engine executes Sequences that are made up of Statements. These statements or instructions can operate on different resources in real-time. HVI can operate on following resources:

- · HVI Actions.

- . HVI Events.

- HVI Triggers.

- Clock signals.

- HVI registers.

- FPGA sandbox registers and memory-maps.

#### **Actions**

HVI actions are digital electronic pulsed or level signals that are sent from the HVI engine to control instrument operations. Typically, actions are associated to instrument-specific operations.

For example, in a digitizer module, a StartAcquisition action sends a digital pulse to start an acquisition operation.

#### **Events**

HVI events are digital electronic pulsed or level signals input to the HVI engine that represent state, or an event in the instrument. HVI events are associated with instrument-specific functions. For example, they can be used to trigger instrument operations or, control the execution in an HVI application.

For example, a WaitForEvent statement pauses execution until the Event occurs.

### **Triggers**

Triggers are electronic logic signals shared between instruments, you can use these to initiate operations, communicate states, or communicate information among instruments.

### **Clock signals**

You can use clock signals to synchronize instruments.

#### **HVI Registers**

HVI Registers are very fast access physical memories that are located in the HVI Engines in instruments. HVI Registers can be used as parameters for operations and modified during the sequence execution. You use them in the same way as Variables in a programming language. The number and size of Registers is defined by each instrument.

#### **FPGA Sandbox Registers and Memory-Maps**

For the modules that contain an FPGA with a user-configurable sandbox, HVI can, if the configuration of the module allows it, access (read/write) the Registers and memory-mapped locations that you define in that sandbox.

To accomplish that, you must obtain the .k7z file for the FPGA sandbox that was generated by the PathWave FPGA application. This file contains all the necessary information to allow you to access the Registers and the memory-mapped locations by Name.

# HVI Sequences and Statements

You control instruments with HVI Statements. Statements operate on resources such as Actions, Events, and Triggers. There are different types of statements that perform different types of operations. HVI Statements are the building blocks of HVI Sequences. These sequences are compiled in your application and are executed in real-time on the HVI engines.

The following sections describe the different types of sequences and statements.

- HVI Sequences

- HVI Statements

# **HVI Sequences**

An HVI instance consists of HVI sequences, these are the foundations of HVI technology. An HVI sequence is an ordered list of HVI statements with associated timing information. A sequence is executed in a time-deterministic manner by the HVI hardware engine located within an instrument. An HVI instance is made up of one or more sequences that run in parallel and synchronously.

There are two types of sequences:

- · Sync sequence

- · Local sequences

# Sync Sequences

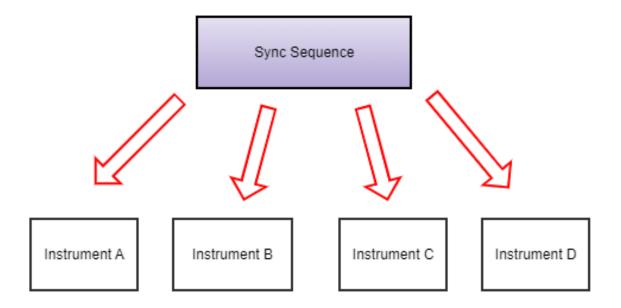

HVI sequences are organized in a hierarchy. A Sync sequence contains commands known as Sync statements that execute across multiple instruments:

## **Local Sequences**

The Local sequences > are executed by each individual HVI engine in an instrument.

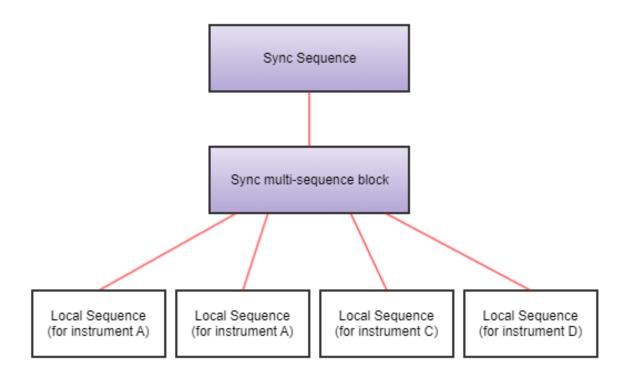

Local sequences are contained within *Sync Multi-Sequence Blocks*. A Sync multi-sequence block is a type of Sync statement that is contained in a Sync sequence.

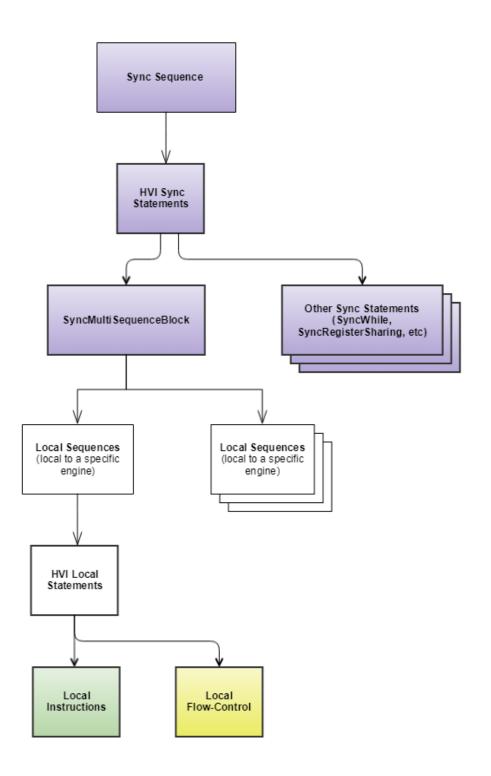

The following diagram shows the relationship between the Sync sequence, Sync multi-sequence block, and Local sequences:

## **HVI Statements**

HVI statements are the commands or operations that make up an HVI sequence. HVI sequences are the ordered lists of HVI statements that are executed with precise timing. If you think of an HVI sequence as a poem, the HVI statements are the possible words you can use to write the poem and the HVI API is the language you use to write it. HVI statements are general-purpose FPGA-level operations that can be executed by the HVI engines.

HVI statements are broadly divided into two groups:

## **HVI Sync statements**

These are used to execute operations or control the flow of execution across all HVI hardware engines. Sync statements are executed synchronously among all HVI engines.

#### **HVI Local statements**

These are the commands or operations you put in the Local sequences to be executed on a specific HVI engine in a specific hardware instrument.

The following diagram shows the different kinds of statements and how they relate to Sync sequences and Local sequences:

# **HVI Sync Statements**

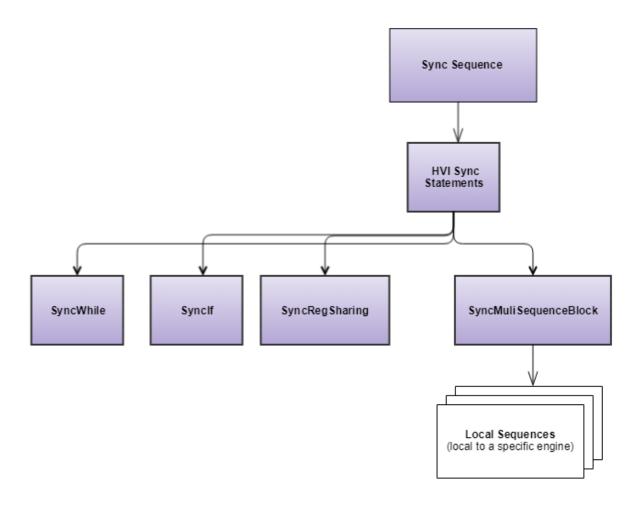

These are used to execute operations or control the flow of execution across all HVI hardware engines. Sync statements are executed synchronously among all HVI engines. For example: Sync While, Sync Registersharing and Sync Multi-Sequence Block.

All HVI Local Sequences operate within HVI Sync statements. The HVI Sync statements determine global or synchronized operations, or synchronization points.

HVI Sync Statements are contained in a Sync sequence. HVI Sync statements execute across all instruments.

The Sync Sequence enables multiple engines to execute statements in lockstep.

The following HVI Sync statements are available:

| Туре                         | Description                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sync While                   | Enables a While loop to execute synchronously on all engines.                                                                                                                                                                                                                                                                                         |

| Sync Multi-Sequence<br>Block | Enables the execution of multiple, simultaneous, engine-specific sequences. Sync multi-sequence blocks are a type of Sync statement that contain a set of Local sequences. The Local sequences execute on individual HVI Engines within the instruments. All Local sequences contained in a Sync multi-sequence block start and end at the same time. |

| Sync Register-Sharing        | Enables you to share data from a source Register to a destination Register in any other HVI Engine.                                                                                                                                                                                                                                                   |

The following diagram shows how the HVI Sync statements fit in the Sync sequence:

## Sync While

The Sync while flow-control enables you to execute a Sync sequence in a loop while a condition is met. The condition is evaluated each time before starting the Sync sequence execution. When the condition is false and the Sync Sequence reaches the end, the Sync while jumps out of the loop and the Sync Sequence containing the Sync while continue the execution with the next Sync statement.

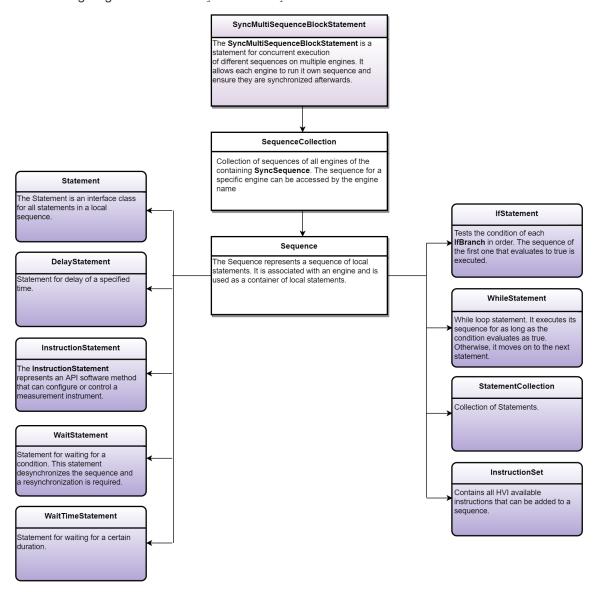

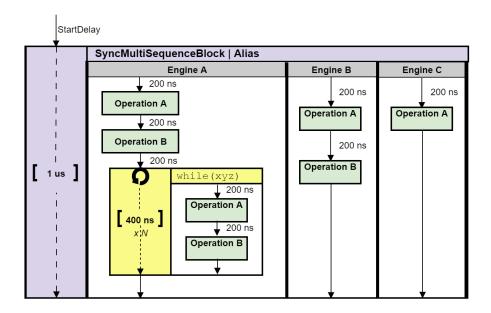

## Sync Multi-Sequence Block

Sync multi-sequence blocks are a type of Sync statement that contain a set of Local sequences. Each Local sequence executes on an individual HVI engine within a specific instrument.

The Sync multi-sequence block enables you to run different sequences on each engine concurrently. It ensures that the execution of all Local sequences starts exactly at the same time and that the Sync sequence remains synchronous afterwards. It serves as a boundary between sections and a container where each engine operates individually.

The Sync Register-sharing statement enables you to share the contents of N adjacent bits from a source Register and write it to a destination Register in another HVI Engine in your HVI.

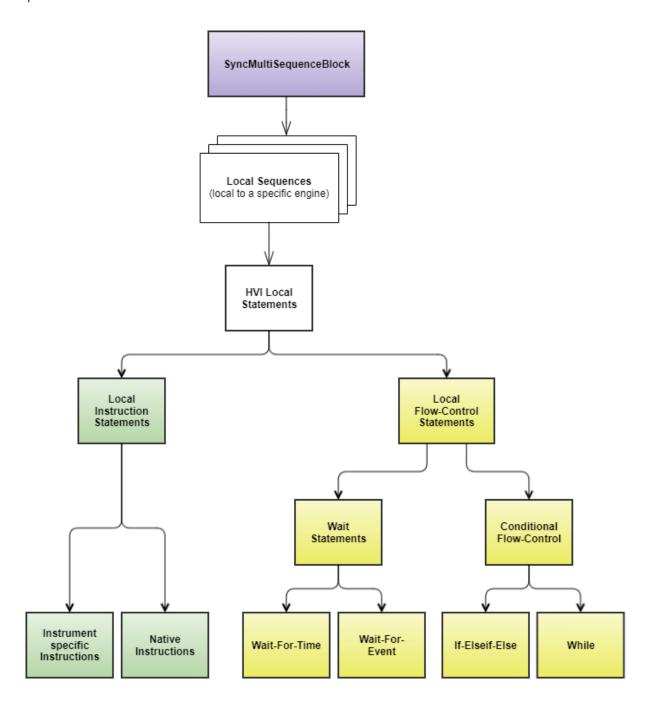

## **HVI Local Statements**

HVI Local statements are the commands or operations that make up Local sequences. These are the commands or operations you put in the Local sequences to be executed on a specific HVI engine in an specific HW instrument. There are two types of Local statements:

- Local Instruction Statements.

- Local Flow-Control Statements.

#### **Local Instruction Statements**

These are operations that are executed by the HVI engine and do not impact the execution flow. They are used to execute HVI-native or instrument-specific instructions. There are two types of Local instruction statements:

#### **HVI-Native Instructions**

HVI-native instructions are present on all instruments for example math operations, writing triggers or executing actions.

## **Instrument-Specific Instructions**

These are instructions that are specific to an instrument. You can use these when you program an HVI with the specific instrument. For example, changing amplitude, queuing waveforms for playback, etc.

## **Local Flow-Control Statements**

Local flow-control statements are used to locally control the execution flow within each Local sequence

These are used to control the execution flow of a specific HVI engine, such as loops and waits. They are divided into two types:

Wait statements:

- · Wait for time.

- Wait for event.

Conditional flow-control statements:

- · While.

- If-Elseif-Else.

The following diagram shows the different types of Local statements and their relationship to the Local sequences:

#### Instruction Statements

Instruction statements are operations that are executed by an HVI engine in the instrument hardware.

There are two types of instructions:

- HVI-native instructions.

- · Instrument-specific instructions.

General purpose HVI-native instructions are defined by the HVI API. These are instrument independent, and general purpose.

Instrument-specific instructions are defined by the HVI instrument add-on API and exposed in each instrument driver, as instrument-specific HVI definitions. Instrument specific instructions can change instrument settings such as amplitude, frequency, or trigger a instrument function such as output a waveform or trigger a data acquisition.

The User Guides for the M320xA PXI AWGs and M310xA PXI DIgitizers describe all the HVI instructions available for each of the M3xxxA PXI instruments.

### Local Flow-Control Statements

Local flow-control is executed within each Local sequence, including Wait statements, loops such as While, and conditional execution like If-Elseif-Else.

This category includes the following types of statements:

- Wait-for-time statements: Wait for an amount of time specified by an HVI Register.

- · Wait-for-event statements: Wait for a condition, currently an event.

- While statement.

- If-Elseif-Else statement.

These statements are depicted with yellow boxs in the flow charts displayed in this User Manual.

All Local flow-control statements except for the Wait statements expose one or more Local Sequences, for instance, While statements have a single sequence, but the If-Elseif-Else statement can have multiple sequences. These statements have the following common characteristics:

- Sequences in flow-control statements can contain any statement including Local flow-control sequences.

- Only Local statements can be added inside Local sequences and consequently inside Local flow-control statements. No Sync statements can be added within Local flow-control statements.

### Wait-For-Time statement

The Wait-time flow control statement causes the sequence to wait for a certain time specified by an HVI Register. Once the time has elapsed, the sequence will continue.

## Wait-For-Event statement

The Wait flow control statement causes the sequence to stop and wait for a condition to evaluate true. Once the condition is true, for example, the selected event occurs, the next instruction is executed. In future releases, this will be extended to more complex conditions.

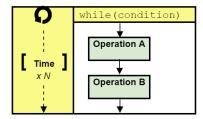

#### While statement

While flow-control is defined by executing the same sequence in a loop while the condition is met.

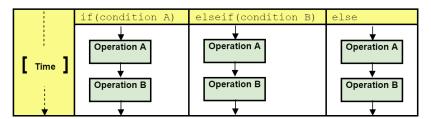

#### If-Elseif-Else statement

The If-Elseif-Else flow control statement is a flow-control statement that conditionally executes different possible Local sequences according to the value of a defined condition.

# **HVI Diagrams**

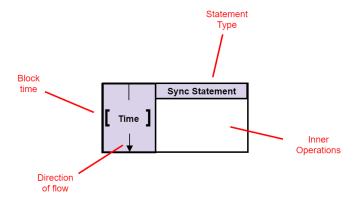

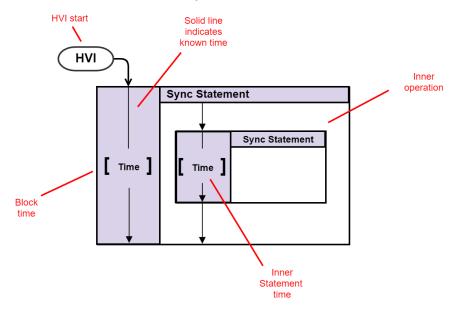

This section shows HVI diagrams. These are used to illustrate HVI sequences.

In the HVI diagrams, colors are used to indicate different kinds of statements:

Statement diagram color code

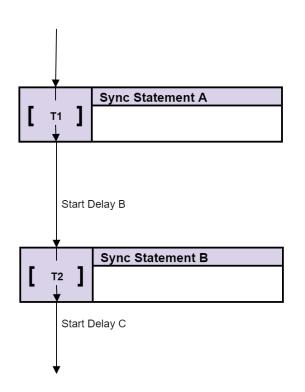

The following diagram shows a single Sync Statement with flow and time for the block:

The diagrams can show nesting of Statements within Statements. For example, the following diagram shows a Sync Statement that is within another Sync Statement:

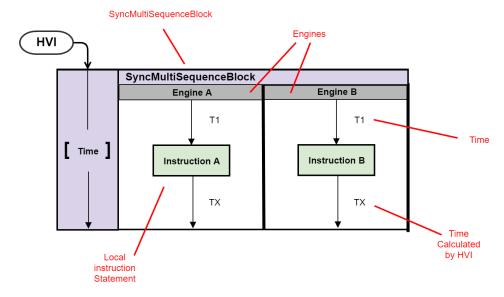

Local Sequences are placed within their Engines in Sync multi-sequence blocks. The following diagram shows a pair of Local Sequences with an instruction each inside a Sync multi-sequence block:

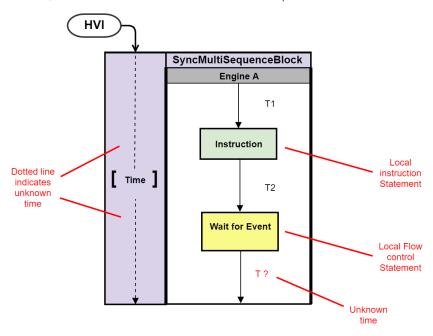

Dotted lines indicate that time is not known at compile time. This is often the case with flow-control statements. In this case the Wait-for-event statement shall not release until the event occurs. It is not known at compile time when this is, so the time cannot be calculated at compile time.

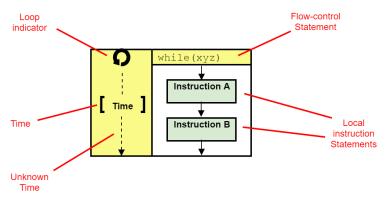

The following diagram shows a Local flow-control statement that encloses a pair of Local instruction statements. The color yellow indicates this is a Local flow-control statement.

The circular symbol is a loop indicator that shows that the block iterates.

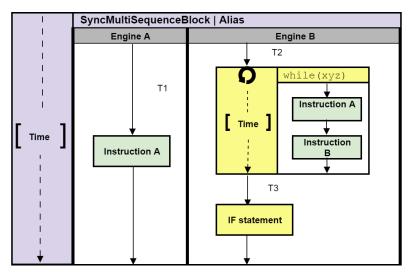

The following diagram shows a more complex example. The Sync multi-sequence block contains two Local sequences, one per HVI Engine. The Local sequences execute operations on their associated HVI engines in parallel.

## **HVI** Timing

This section describes the timing of HVI operations.

# **About HVI Statement Timing**

When you are programming an HVI, you have precise control over the execution timing. To understand the HVI statement execution timing, there are several time definitions that you must understand:

- · Start time.

- End time.

- · Fetch time.

- Execution time.

- Start delay.

#### Start time

This is the instant of time when HVI starts the execution of a statement. Start time is specified by the user during sequence creation, with the **start delay.** HVI exactly meets the specified time or generates an error if it is not possible.

#### End time

This is the instant of time when the statement execution is completed and the result is available, or the operation took place (update Registers, trigger value changing, ...). In the case of operations that have a long execution time, for instance <code>Arb play</code>, the execution time indicates when the first sample of the Arb data starts flowing out.

#### Fetch time

This is the time interval required by the HVI engine to fetch and dispatch a statement for the actual execution. Depending on the statement or instruction characteristics, for instance, the number of parameters, a statement may take several HVI engine cycles to complete the fetch before the actual execution can start.

#### **Execution time**

This is the time interval from the **Start time** until the **End time** of the statement. This interval is determined by product constraints and inherent limits, such as propagation delays and resource availability.

### Start delay

Start delay is controlled by the user and defines a waiting period between the execution of consecutive statements. The start delay is a parameter in the <code>add\_statement()</code> methods. This ensures there is enough time for correct execution and allows you to have full control of timing of the operations. If the start delay is not accounted for properly, the HVI sequences misbehave.

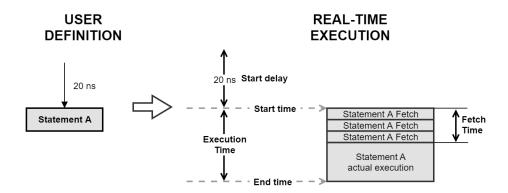

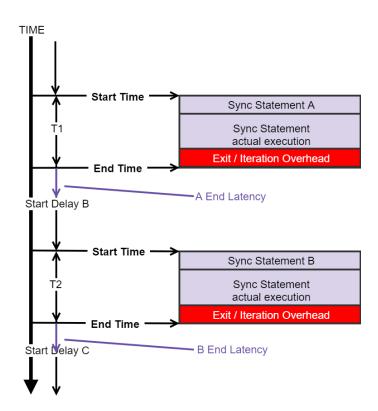

The following diagram shows these definitions:

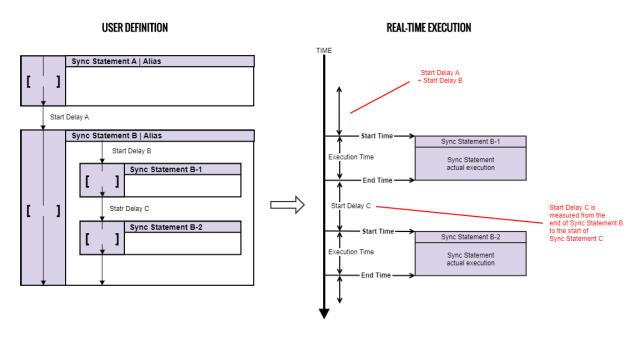

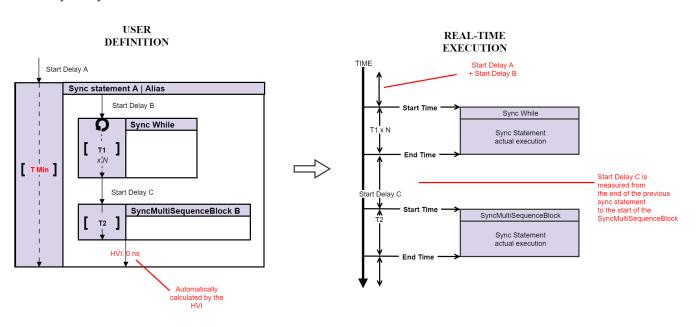

## Sync Statement timing

For Sync statements, the **Start delay** is measured from the end of one Sync statement to the start of the following Sync statement.

The following diagram shows the timing between Sync statements. The diagram shows two Sync statements, A and B. Sync statement B is a container for two further Sync statements, B-1 and B-2. The times indicated are **Start Delay A**, **Start Delay B**, **Start Delay C**, T1, and T2.

The time between the end of Sync statement A and the start of Sync statement B-1 is **Start Delay A+ Start Delay B**.

The time between the end of Sync statement B-1 and the start of Sync statement B-2 is Start Delay C.

## Sync-Statement timing

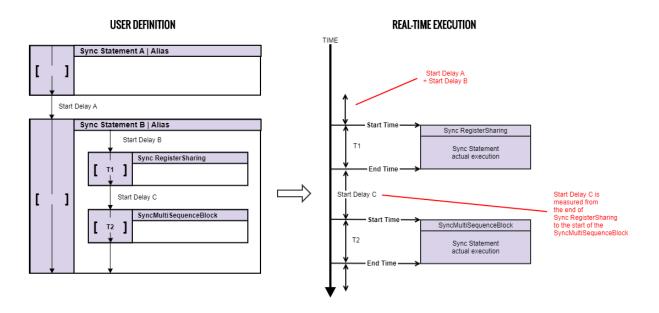

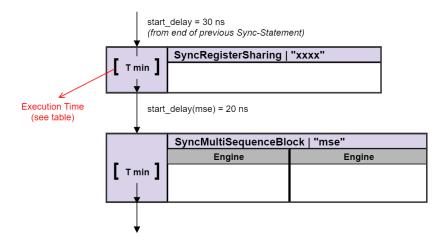

Sync Register-Sharing and Sync Multi-Sequence Block Timing

For the timing of the Sync statement types Sync Register-sharing and Sync multi-sequence block is the same as most Sync statements. The Start delay is measured from the end of one Sync statement to the start of the next Sync statement.

The following diagram shows the timing between a number of Sync Statements including Sync Registersharing and Sync multi-sequence block.

The diagram shows two Sync Statements A and B. Sync Statement B is a container for 2 further Sync Statements Sync Register-sharing and Sync multi-sequence block. The times indicated are **Start Delay A**, **Start Delay B**, **Start Delay C**, T1, T2, and T3.

The time between the end of Sync Statement A and the start of Sync multi-sequence block is **Start Delay A + Start Delay B**.

The time between the end of Sync Register-sharing and the start of Sync multi-sequence block is **Start Delay C**.

### Sync Register-sharing and Sync multi-sequence block timing

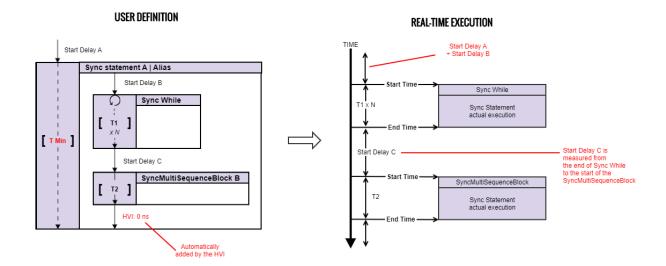

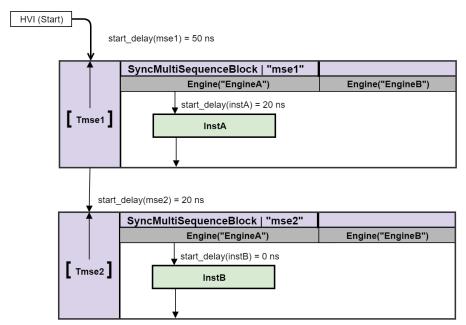

## Sync While

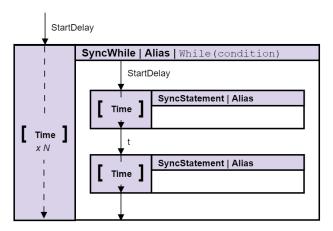

For the Sync flow-control Statement Sync while, the timing is different compared to other Sync statements. The Sync while statement continues operation while a condition is met. It stops executing when the condition is no longer met.

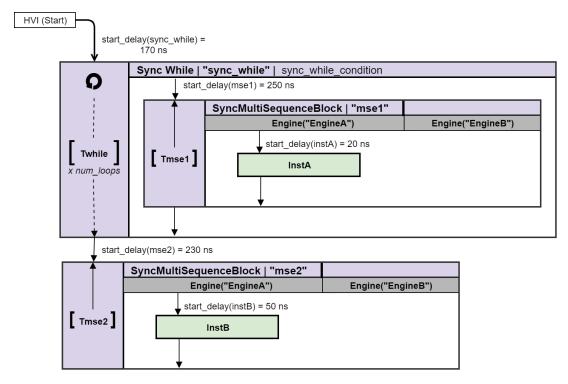

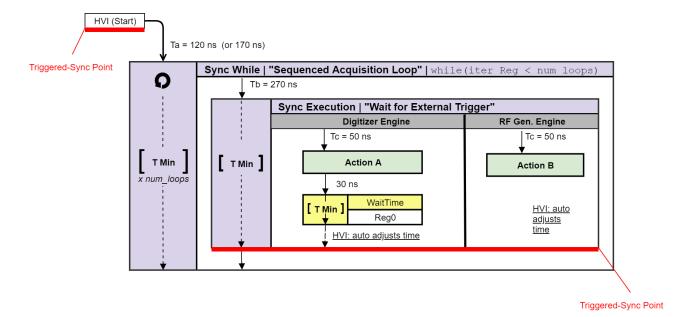

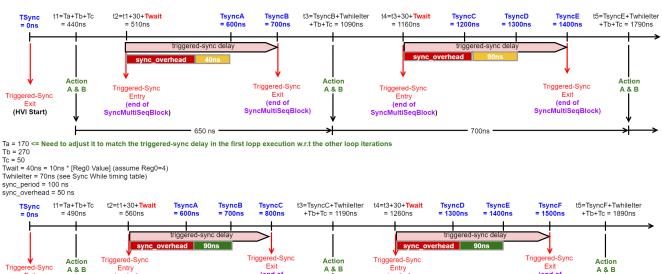

The following diagram shows a Sync while statement with other Sync statements. The time for an iteration of Sync while is  $\mathbf{T2} \times \mathbf{N}$ , where  $\mathbf{T2}$  is the time per iteration and  $\mathbf{N}$  is the number of iterations. The time cannot be indicated exactly on a diagram or in code, because the number of iterations is not known until runtime.

The time for the containing statement Sync statement A cannot be indicated if it contains a flow-control statement. This is indicated by the dotted line and the time indicated as **T min**.

The time between the end of the Sync multi-sequence block B and the end of Sync statement A is 0 ns.

## Sync While

# **Local Statement Timing**

This section describes the timing of local statements.

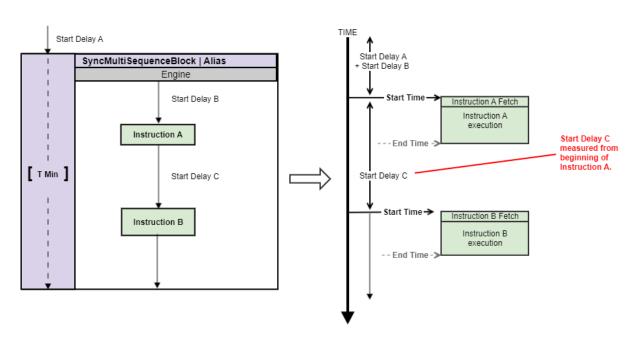

Local Instruction Timing

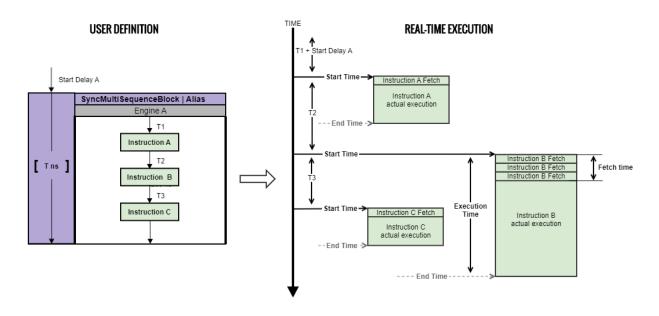

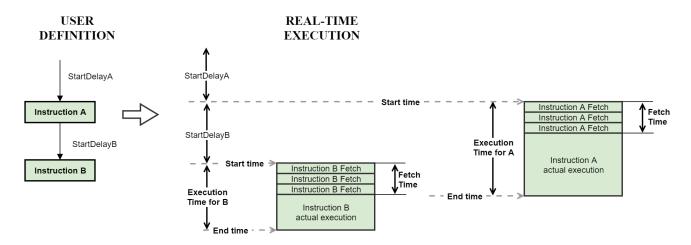

The following diagram shows the timing of Local instructions.

For instructions, the following Start Delay is measured from the start of the instruction. This is possible because once the instruction fetch cycles are completed, the HVI engine is free to fetch and execute another instruction.

The following diagram shows two instructions and their timing.

## local Instruction timing

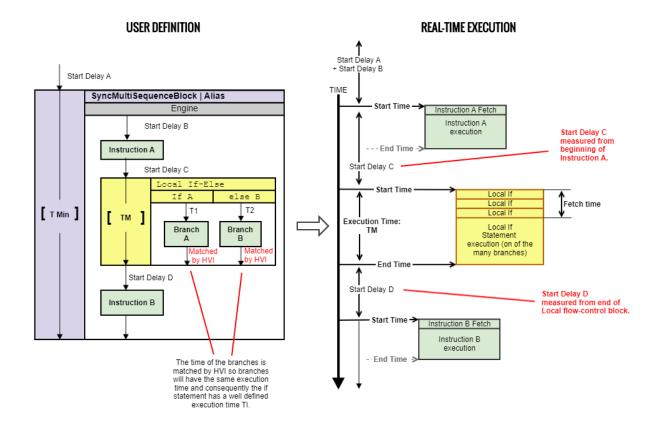

# USER DEFINITION REAL-TIME EXECUTION

## Overlapping Instruction timing

The execution of instructions can overlap. This is shown in the following diagram.

Instruction B starts execution, then after a delay of T3, instruction C starts execution while instruction B is still executing. Instruction B is still executing when instruction C finishes.

The overlap of instructions is possible when there is no overlapping fetch. It is important to consider the effects of overlapping instructions execution, because the result of the first instruction is not effective or available when the overlapping instruction finishes its fetch cycles and starts execution.

## **Overlapping Instructions**

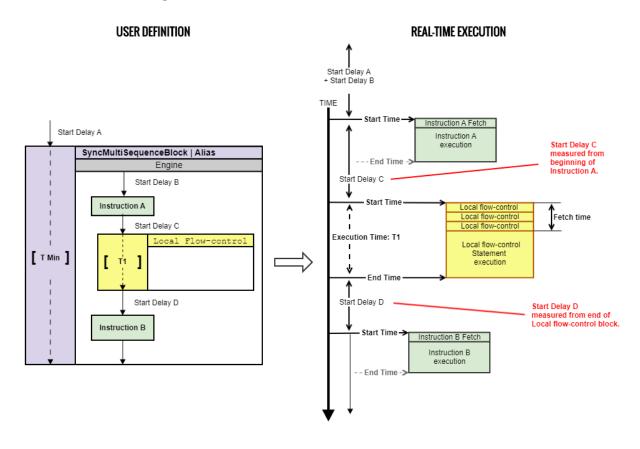

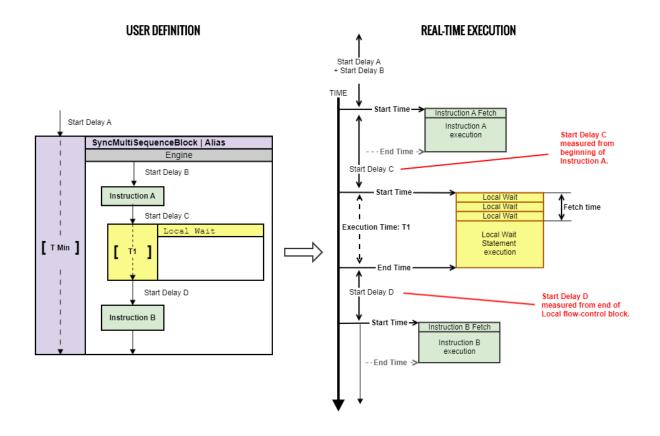

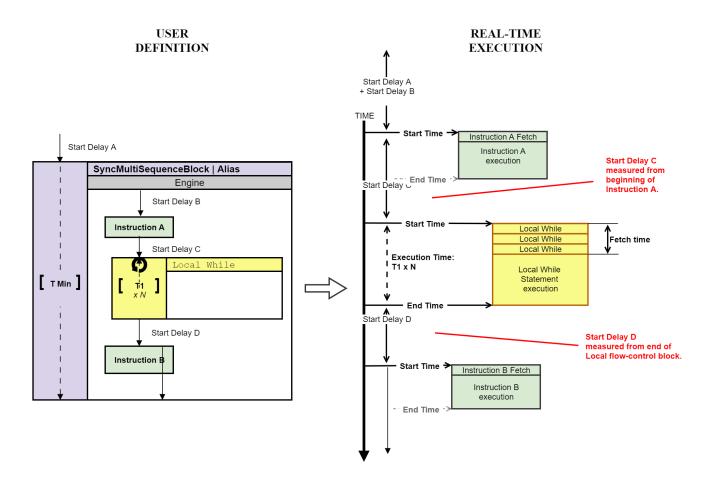

## Local Flow-Control Timing

For Local flow-control operations, the Start delay of the next statement is measured from the end of the flow-control statement. As with Sync flow-control statements, the HVI engine is busy during the execution of the flow-control statement. No overlapping is possible between flow-control statements and any other statements. The following diagram shows the difference between measuring timing of instructions and Local flow-control operations.

For instructions, the Start delay of the next statement is measured from the start of the instruction, while for the local flow-control statements, Start delay D is measured from the end of the flow-control block.

The dotted line indicates that the execution time of the Local flow-control block T1 is not known at compile time.

## Local flow-control timing

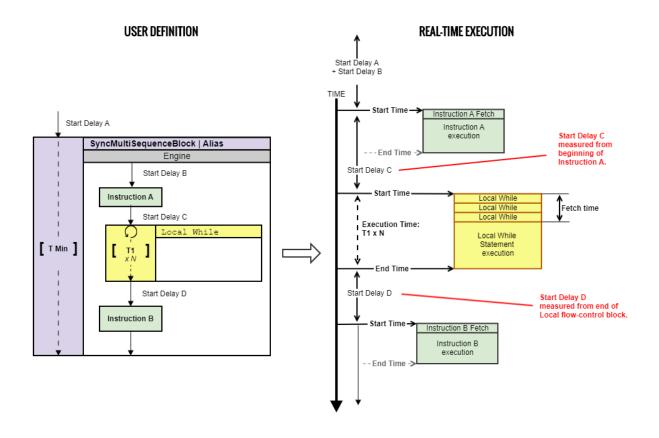

### Local While

The Local while statement continues execution while a condition is met and finishes execution when the condition is no longer met. This is the same as timing of Sync while statements.

The following diagram show a Local while statement with other instructions.

The time for an iteration of Local while is  $T1 \times N$ , where T1 is the iteration time and N is the number of times it iterates. The time cannot be indicated exactly on a diagram or in code because the number of iterations is not known until runtime.

For Local while statements, the following Start delay is measured from the end of the Local while statement. In the following diagram, Start delay D is measured from the end of the Local while statement.

The dotted line indicates that the execution time of the Local while block T1 is not known at compile time.

#### **Local While**

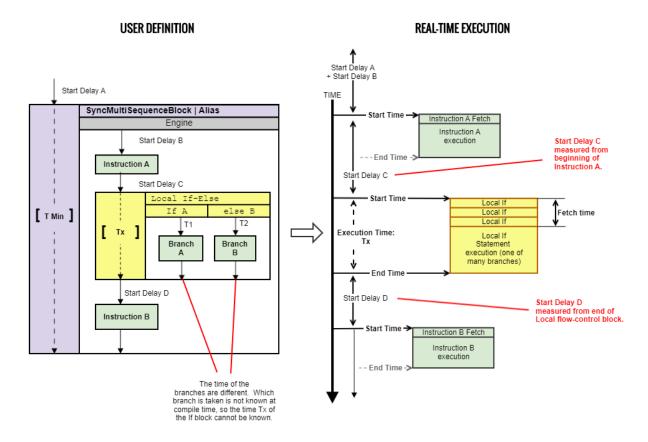

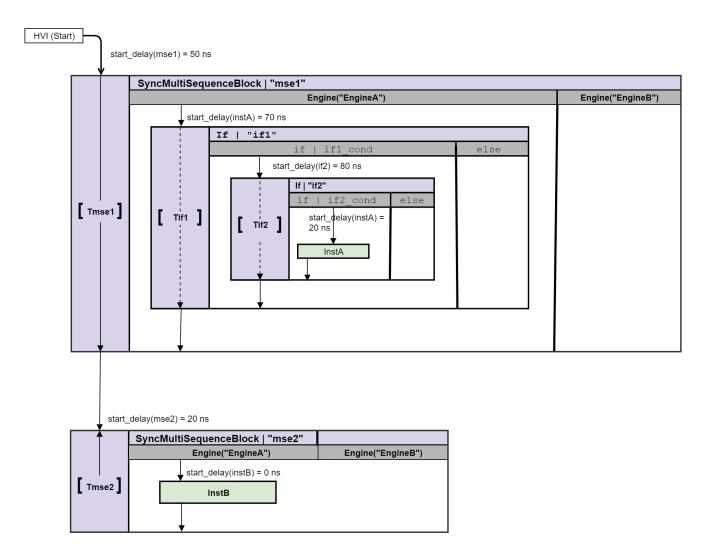

### Local If

For Local if statements, the following Start delay is measured from the end of the Local If statement. As with Sync while statements, the time taken is only known at runtime, so it is not possible to indicate them on a diagram or in code.

This following diagram shows the timing of Local if statements. The Start delay D is measured from the end of the Local if statement.

The Local If has two branching options with times TI 1 and TI 2. These times can be different. Since the choice of branch is not known at compile time, the time for the Local If block cannot be known.

The line for the Local if block is dotted. This indicates that the execution time of the Local If block Tx is unknown. The time of the containing block is also therefore unknown, and it is also dotted. The time of the Sync multi-sequence block is indicated as T min.

#### **Matched Branches**

Unlike other flow-control options, the Local if statements can have different execution paths each with different times. The *matched branches* option enables you to control how the HVI deals with them.

Enabling matched branches ensures the HVI synchronizes the times of the branches, so they are the same. The shorter branches get an additional delay added when they are finished so that the duration of all branches is equal. If the matched branches option is not enabled, the branches can end at different times, that is, they are de-synchronized.

In the following diagram the branches in the If-else statement are matched. This ensures the Local if ends at the same time irrespective of the branch taken.

The total branch time is marked with the time TM, this represents the matched time. The choice of branch is not known at compile time, but since the times are matched the time TM is known.

The times are known at compile time so the timelines of the local If block and and the containing Sync multisequence block are both solid.

## Local Wait (event or time in Register)

For Local wait statements, the following Start delay is measured from the end of the Local wait statement. As with Sync while statements, the time taken is only known at runtime, so it is not possible to indicate them on a diagram or in code.

The following diagram shows the timing of a Local wait statement. The following Start delay D is measured from the end of the Local wait statement.

The execution time of the Local wait statement T1 is not known at compile time, this is indicated by the dotted line.

The time of the Sync multi-sequence block is indicated as T min. The dotted line indicates an unknown time.

#### **Local Wait**

# HVI time matching for Sync Statements

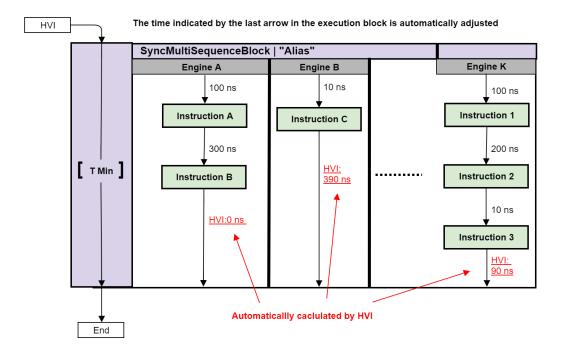

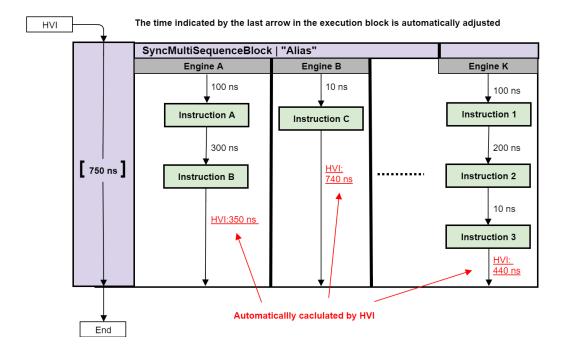

# Sync Multi-Sequence Block Time Matching

In a synchronized multi-sequence block, you can define the statements that the HVI engines on instruments, execute in parallel with the other engines.

Local sequences start and end their execution within the Sync multi-sequence block synchronously. You can define the exact start time of each Local statement after the previous one.

HVI automatically calculates the execution time of each local sequence and adjusts the execution of all local sequences within the Sync multi-sequence block. This is so that the sequences within the Sync multi-sequence block can all end together deterministically. The final time is calculated automatically.

There are two cases that are treated in a different way by HVI:

- Execution time is known at HVI compilation time for all Local Sequences within the Sync multi-sequence

- Execution time is unknown at HVI compilation time for one or more local Sequences within the Sync multisequence block.

## Known time (Sync execution)

When all Local sequences contain instructions or flow-control statements with an execution time that is known at HVI compilation time, the HVI accounts for the different execution time of all local sequences during compilation and adjust the final times so each Local sequence reaches the end of the Sync multi-sequence block at the same time.

## Sync multi-sequence block with minimum execution time

In the following diagram, the time of the Sync multi-sequence block is not specified, so the compiler will adjust the total execution time of all Local sequences to the longest one. The times of the instructions and the delays between them are known, so the timing between them and the timing of the entire block can be calculated. The Sync multi-sequence block execution time is set to the minimum possible time given by the longest Local sequence.

The total time for Engine A is 400 ns and HVI calculates the times required for the other engines to finish at the same time. For Engine B this is 390 ns, for Engine K this is 90 ns.

Sync multi-sequence block with a specific execution Time

In the following diagram, the times of the instructions and the delays between them are known, so the timing between them and for the entire block can be calculated. In this case the total time is specified at 750 ns. The HVI calculates the times required for all the other engines to finish at the same time. For Engine A this is 350 ns, For Engine B this is 740 ns, for Engine K this is 440 ns.

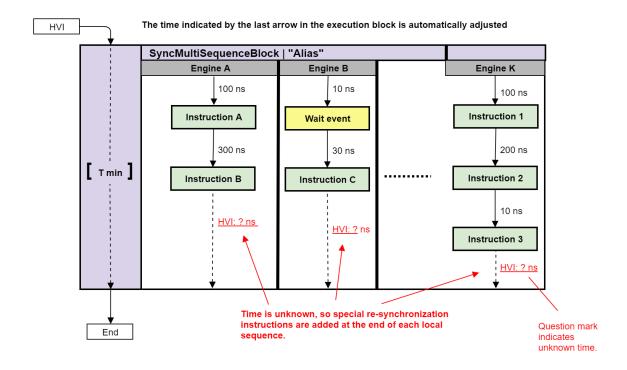

## Unknown time (re-synchronization)

In some cases, one or more of the local sequences within the Sync multi-sequence block include a local flow-control statement that has an execution time that is unknown at HVI compilation time. At the point in the Local sequence where the unknown execution time is encountered, the Local sequence becomes de-synchronized. Since HVI ensures that all the Local sequences in a Sync multi-sequence block end at the same time when there is such a Local flow-control statement, HVI implements a special re-synchronization procedure at the end of the Sync multi-sequence block.

In the following diagram, the time of the instructions and the delays between them are known except for the execution time of the Wait event. This means the execution time of the complete Sync multi-sequence block cannot be specified. HVI still enforces all Local sequences to end at the same time, but in this case the time required at the end of each sequence is not known since it cannot be calculated during the HVI compilation, this is indicated by the dotted lines. The time of the full Sync multi-sequence block is also unknown so this is indicated as T min with a dotted line. To enforce that all Local sequences synchronize again at the end of the Sync multi-sequence block, special re-synchronization instructions are added at the end of each local sequence in the Sync multi-sequence block. This re-synchronization procedure relies on triggering resources to re-synchronize the execution of the Local sequences on all the HVI engines.

# Chapter 5: The HVI API

This chapter describes the HVI API. It describes the main classes required to understand the key programming concepts you must understand when you are defining an HVI implementation.

The HVI API is a class-based API, it is a combination of the HVI API and the HVI instrument add-on API:

- The HVI API is the common API used by any instrument that supports HVI.

- The HVI Instrument add-on API is an instrument-specific API that complements the HVI API.

The HVI API functions are not sufficient to fully execute HVI sequences on an instrument. To successfully run an HVI, both APIs must be used.

This chapter contains the following sections:

- HVI API Functionality

- HVI API Organization

- SystemDefinition

- Sequencer

- Hvi

# HVI API Functionality

This section describes the functionality that is common across the HVI API. It contains the following sections:

- HVI API capabilities.

- HVI Collections.

- HVI API Error Management.

## **HVI API Capabilities**

The HVI API provides many capabilities. The capabilities that are available through the HVI API include:

- · Chassis/PXI backplane resource configuration.

- · Interconnect configuration, for example, with M9031A modules.

- · Access to HVI memory resources in the FPGA user Sandbox.

- · Real-time sequencing:

- Synchronized flow-control, for example, While loops.

- Synchronized multi-sequence block statements that provide access to local instructions and flow control.

- Local flow-control, such as While loops and If statements.

- Local Instructions and operations. These include HVI-native instructions and instrument-specific instructions.

## **HVI Collections**

Resources in HVI are grouped into Collections. Collections group items of the same type, such as:

- Engines.

- Triggers.

- Actions.

- Registers.

- FpgaSandboxes.

Class collections are particularly useful because a member instance can be accessed by index or string.

Collections are found within the sequence hierarchy with their corresponding local or synchronized functions.

The concept of collections is fundamental in the HVI API use model because every component used within the HVI must be registered with a collection. If the component is not registered, it cannot be used. To register components, add them to the collection of items of that function, for example, you must add triggers to a trigger collection.